## Diseño e implementación en FPGA de un filtro Kalman para aplicaciones biomédicas

Trabajo Fin de Grado Grado en Ingeniería de Computadores

> Fernando Capellán Pizarroso Simona Florina Puica Daniel Sánchez Huerta

> > Dirigido por

Oscar Garnica Alcázar Juan Lanchares Dávila

Departamento de Arquitectura de Computadores y Automática Facultad de Informática Universidad Complutense de Madrid

**Junio 2015**

$\label{eq:control_exp} Documento\ maquetado\ con\ TEX^IS\ v.1.0+.$

## Diseño e implementación en FPGA de un filtro Kalman para aplicaciones biomédicas

Trabajo fin de grado Grado en Ingeniería de Computadores

Autores

Fernando Capellán Pizarroso Simona Florina Puica Daniel Sánchez Huerta

Directores

Oscar Garnica Alcázar Juan Lanchares Dávila

Departamento de Arquitectura de Computadores y Automática Facultad de Informática Universidad Complutense de Madrid

**Junio 2015**

### Autorización

Los autores de este proyecto autorizan a la Universidad Complutense de Madrid a difundir y utilizar el presente trabajo de investigación, tanto la aplicación como la memoria, únicamente con fines académicos, no comerciales y mencionando expresamente a sus autores. También autorizan a la Biblioteca de la UCM a depositar el trabajo en el Archivo Institucional E-Prints Complutense.

#### Autores

Fernando Capellán Pizarroso Simona Florina Puica Daniel Sánchez Huerta

La mejor forma de predecir el futuro es implementarlo. David Heinemeier Hansson

## Agradecimientos

No nos habría sido posible realizar este proyecto de no haber contado con todo el apoyo y cariño de todas las personas que nos rodean. En primer lugar queremos agradecer a nuestros directores Juan y Óscar por habernos propuesto este proyecto y por habernos guiado y aconsejado a lo largo de su desarrollo. En segundo lugar dar las gracias a todos los profesores que, a lo largo de tantos años de carrera, nos han transmitido los conocimientos necesarios para poder llevarlo a cabo. Por último y no menos importante, a nuestros familiares, parejas, amigos y compañeros, los cuales nos han acompañado a lo largo de esta odisea.

A todos vosotros. Gracias.

#### Resumen

La Diabetes Mellitus tipo 1 es una enfermedad crónica caracterizada por la incapacidad del páncreas de producir insulina. Esta hormona regula la absorción de la glucosa del torrente sanguíneo por parte de las células. Debido a la ausencia de insulina en el cuerpo, la glucosa se acumula en el torrente sanguíneo provocando problemas a corto y largo plazo, como por ejemplo deterioro celular.

Los pacientes con esta enfermedad necesitan controlar su glucemia (concentración de glucosa en sangre) midiendo la misma de forma regular e inyectándose insulina subcutánea de por vida. Para conocer la glucemia se pueden utilizar Monitores Continuos de Glucosa (MCG), que proporcionan el valor de la glucosa intersticial cada 1-5 minutos. Los MCG actuales presentan los siguientes problemas:

- El sensor que llevan incorporado introduce ruidos asociados a la medición y se degrada a lo largo de su vida útil, lo que dificulta la interpretación de los datos obtenidos.

- Debido al transporte de la glucosa desde el torrente sanguíneo hacia el fluido intersticial, el valor de la glucosa en este último presenta cierto retraso frente al valor de la glucosa en el primero.

- Es necesaria una calibración frecuente, usando como referencia la glucosa en sangre muestreada del propio paciente.

- La variabilidad de la glucosa entre distintos pacientes y a lo largo de la vida de un mismo paciente dificulta el ajuste de los parámetros de los filtros.

Una solución propuesta actualmente es la utilización de filtros Kalman. Éstos se describen mediante algoritmos recursivos capaces de identificar el estado oculto (glucosa en sangre) a partir de medidas indirectas del mismo (glucosa intersticial), y al mismo tiempo predicen su comportamiento futuro y eliminan el ruido de la señal.

El principal problema de esta propuesta es que su implementación se realiza en software, y por tanto, trabajan con datos ya procesados por el XII RESUMEN

sensor. Esto puede agravar alguno de los problemas listados con anterioridad e impide sacar el máximo provecho a la gran capacidad de estos filtros.

Este proyecto surgió con la idea de dejar atrás los filtros Kalman software y sustituir los filtros digitales hardware con los que actualmente cuentan los sensores por un filtro de Kalman. En este proyecto se implementa sobre una FPGA un filtro Kalman de tres estados (glucosa, velocidad de variación de la glucosa y aceleración de la velocidad de dicha variación), teniendo como entrada medidas reales proporcionadas por un MCG.

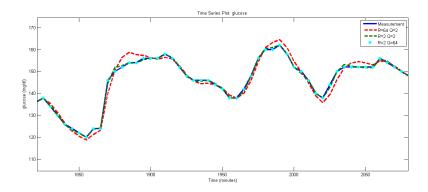

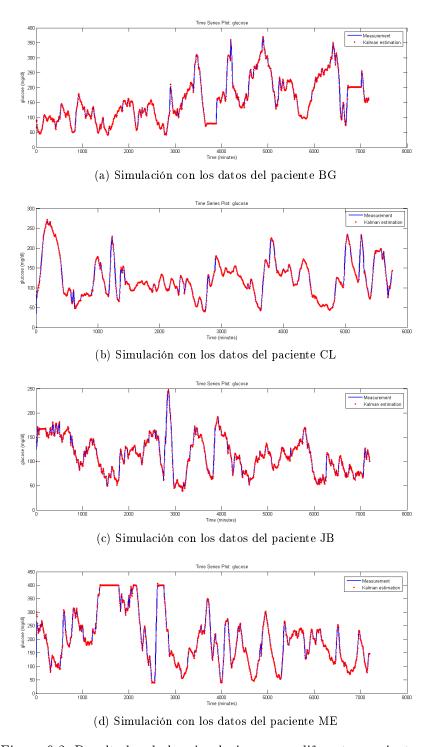

En los resultados se puede comprobar que las predicciones realizadas por el filtro Kalman implementado en este proyecto se ajustan perfectamente al comportamiento de la glucosa en sangre. Se han realizado simulaciones del filtro para observar su respuesta ante variaciones bruscas de la glucosa y la fiabilidad de la misma durante un largo periodo de tiempo. Para ello se han utilizado medidas de cuatro pacientes reales. En aquellos cuya glucosa cambia de forma brusca se puede observar que el filtro estima el valor de ésta erróneamente. A pesar de ello, utiliza este resultado incorrecto para corregir la siguiente predicción y ofrecer resultados correctos en el futuro.

Palabras clave: FPGA, Filtro de Kalman, Páncreas Artificial, Diabetes Mellitus, Diseño Hardware, Algoritmo recursivo, Procesado de señal.

### Abstract

Diabetes Mellitus type 1 is a chronic disease characterised by the inability of the pancreas to produce insulin. This hormone controls the absorption of glucose from the bloodstream by the cells. As a result of the absence of insulin in the body, glucose builds up in the bloodstream causing short and long term problems. Cellular degeneration serves as an example.

Patients with this disease need to keep their glycemia under control by measuring it regularly and injecting subcutaneous insulin for the rest of their lives. An option to know the blood glucose concentration is the use of a continuous glucose monitoring, as the provide the interstitial glucose value every 1 to 5 minutes. Current CGMs present the following problems:

- The sensor they have embedded adds measurement-related noises and deteriorates during its lifespan, rendering the interpretation of the gathered data more difficult.

- There is a delay between the concentration of blood glucose and interstitial glucose due to the fact that it has to be transported from one environment to another.

- Frequent calibration is required, using the blood glucose measured from the patient as reference.

- Glucose variability between patients and in a sole patient's lifetime makes difficult to adjust the filter parameters.

A proposed solution is the use of Kalman filters. They are described by recursive algorithms capable of identifying the hidden state (blood glucose) from indirect measurements of itself (interstitial glucose), predicting, at the same time, its future behavior and removing the noise from the signal.

The main problem these proposals share is that the implementation is done in software, and thus, they work with data that has already been processed by the sensor. This can worsen some of the problems listed above, and prevents the filters from delivering their full potential.

This project's goal is to leave behind Kalman filters implemented in software and to replace the digital hardware filters that sensors currently equip XIV ABSTRACT

with a Kalman filter. In this project, a Kalman filter with three states (glucose, glucose variation speed and acceleration of the speed of said variation) is implemented on an FPGA, with real measurements provided by a CGM.

Experimental results show that the estimations made by the Kalman filter implemented throughout this project match precisely the behavior of the blood glucose. Simulations of the filter have been done to observe its response in the presence of sharp variations of glucose and its reliability during long periods of time. For this, measurements from four real patients have been used. When glucose experienced a sudden change, the filter can be seen mispredicting the next value. Despite this, it uses this incorrect result to correct the next estimation and deliver precise results in the future.

**Keywords**: FPGA, Kalman filter, Artificial Pancreas, Diabetes Mellitus, Hardware design, Recursive algorithm, Signal processing.

## Índice

| Αι | utorización                                                                                                                                                                           | V                                |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Αę | ${f gradecimientos}$                                                                                                                                                                  | IX                               |

| Re | esumen                                                                                                                                                                                | ΧI                               |

| A۱ | bstract                                                                                                                                                                               | XIII                             |

| Ι  | Estado del arte                                                                                                                                                                       | 1                                |

| 1. | Motivaciones del trabajo                                                                                                                                                              | 3                                |

| 2. | Teoría del filtro Kalman  2.1. Ecuaciones generales para el filtro de Kalman discreto  2.1.1. Ecuaciones de los modelos de proceso y medición  2.1.2. Ecuaciones del Filtro de Kalman | 7<br>8<br>8<br>9<br>10           |

| 3. | Modelo del Filtro de Kalman propuesto por Palerm                                                                                                                                      | 13                               |

| II | Implementación                                                                                                                                                                        | 17                               |

| 4. | Módulo Filtro de Kalman4.1. Representación de los datos4.2. Funcionamiento general4.3. Datos intercambiados y constantes4.4. FIFOs4.5. Protocolo de comunicación                      | 19<br>20<br>22<br>22<br>24<br>25 |

| 5. | Módulos Comunes         5.1. Generadores de direcciones                                                                                                                               | <b>31</b> 31                     |

| XVI | ŕ      |

|-----|--------|

|     | INDICE |

|    | 5.2. Operadores                                             | 33  |

|----|-------------------------------------------------------------|-----|

|    | 5.3. Memorias RAM                                           | 39  |

| 6. | Módulo Prediction                                           | 41  |

|    | 6.1. Inicio de la predicción                                | 43  |

|    | 6.2. Cálculo de XPR: módulo $i\_calc\_x$                    | 43  |

|    | 6.3. Cálculo de PPR: módulo $i\_\mathit{calc}\_p$           | 49  |

| 7. | Módulo Gain                                                 | 57  |

|    | 7.1. Cálculo de la ganancia                                 | 58  |

| 8. | Módulo Correction                                           | 67  |

|    | 8.1. Cálculo de XPO: módulo $i\_state\_correction$          | 74  |

|    | 8.2. Cálculo de PPO: módulo i_covariance_correction         | 81  |

| 9. | Resultados experimentales                                   | 87  |

|    | 9.1. Ajuste de los parámetros $Q$ y $R$                     | 87  |

|    | 9.2. Simulaciones con datos reales                          | 89  |

| 10 | Síntesis                                                    | 91  |

|    | 10.1. Configuración de la herramienta                       | 91  |

|    | 10.2. Análisis del informe de síntesis                      | 91  |

|    | 10.3. Camino crítico                                        | 93  |

| ΙΙ | Conclusiones y trabajo futuro                               | 95  |

| 11 | Conclusiones                                                | 97  |

| 12 | Conclusions                                                 | 99  |

| 13 | Futuras líneas de trabajo                                   | 101 |

|    |                                                             |     |

| IV | Apéndices                                                   | 103 |

| Α. | Representación Aritmética                                   | 105 |

|    | A.1. ¿Qué es punto fijo?                                    | 105 |

|    | A.2. Operar en punto fijo                                   | 105 |

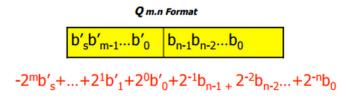

|    | A.3. Notación $Q$                                           |     |

|    | A.3.1. Determinación de $m$ y $n$ en una notación $Q_{m.n}$ |     |

|    | A.3.2. Aritmética en notación $Q$                           | 107 |

| В. | Herramientas utilizadas                                     | 109 |

| XVII |

|------|

| 111  |

| 113  |

| 115  |

|      |

# Índice de figuras

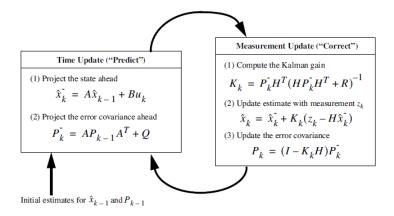

| 2.1. | Sistema de predicción-corrección con las ecuaciones de cada etapa             | 10 |

|------|-------------------------------------------------------------------------------|----|

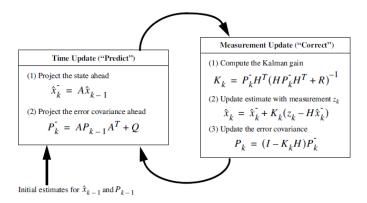

| 3.1. | Sistema de predicción-corrección con las ecuaciones del mode-<br>lo de Palerm | 15 |

|      | lo de Falerin                                                                 | 19 |

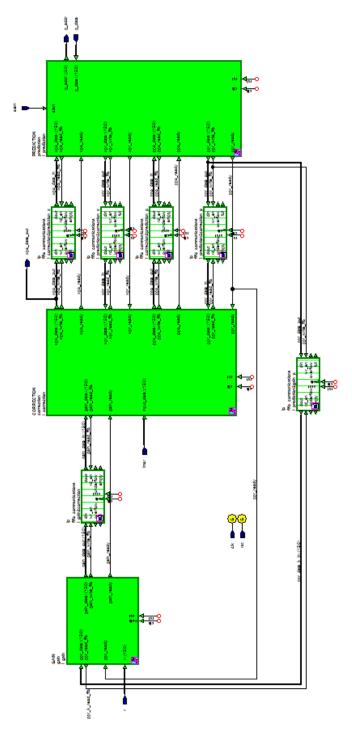

| 4.1. | Módulo Filtro de Kalman a nivel top                                           | 21 |

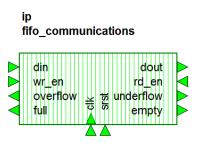

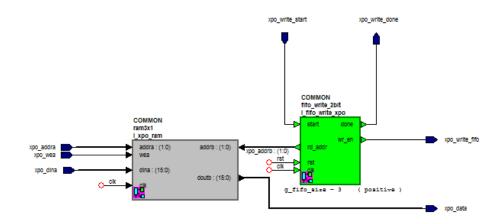

| 4.2. | Interfaz de las FIFOs utilizadas en el diseño                                 | 24 |

| 4.3. | Protocolo de comunicación mediante FIFOs                                      | 26 |

| 4.4. | Módulo encargado de la escritura de las FIFOs                                 | 26 |

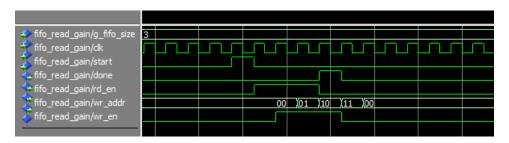

| 4.5. | Cronograma de la escritura de las FIFOs                                       | 27 |

| 4.6. | Módulo encargado de la lectura de las FIFOs                                   | 28 |

| 4.7. | Cronograma de la lectura de las FIFOs                                         | 29 |

| 5.1. | Ejemplo de módulo generador de direcciones                                    | 32 |

| 5.2. | Módulo sumador 3x3                                                            | 33 |

| 5.3. | Módulo restador 3x3                                                           | 34 |

| 5.4. | Módulo multiplicador 3x3 con 3x3                                              | 35 |

| 5.5. | Módulo que realiza la división                                                | 38 |

| 5.6. | Cronograma de la escritura/lectura en una RAM $\dots$                         | 40 |

| 6.1. | Top-level del módulo Prediction                                               | 41 |

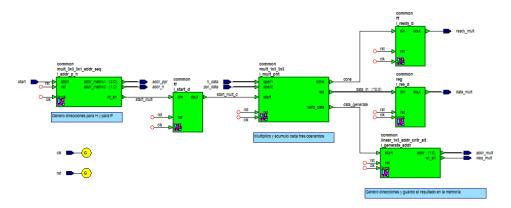

| 6.2. | Diagrama de bloques del módulo $i\_calc\_x$                                   | 44 |

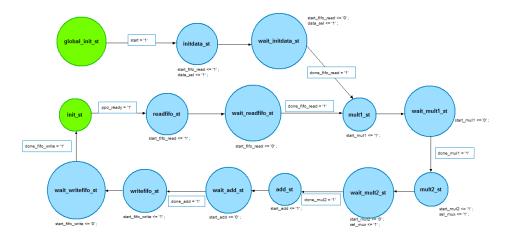

| 6.3. | Unidad de control del módulo $i\_calc\_x$                                     | 45 |

| 6.4. | Diagrama de bloques del módulo $i\_mult\_ax$                                  | 47 |

| 6.5. | Diagrama de bloques del módulo $i\_calc\_p$                                   | 50 |

| 6.6. | Unidad de control del módulo $i\_calc\_p$                                     | 51 |

| 7.1. | Top-level del módulo Gain                                                     | 58 |

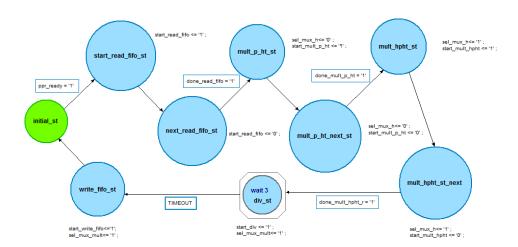

| 7.2. | Unidad de control del módulo GAIN                                             | 60 |

| 7.3. | Diagrama de bloques del módulo $i\_mult\_p\_ht$                               | 63 |

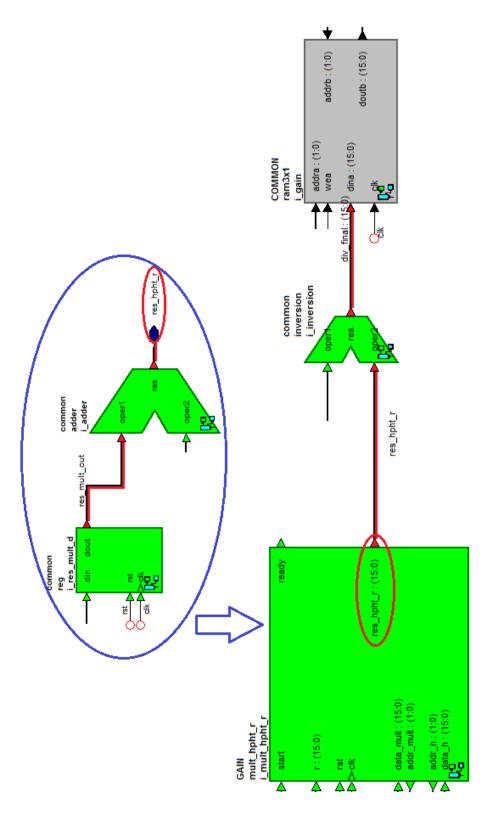

| 7.4. | Diagrama de bloques del módulo $i\_mult\_hpht\_r$                             | 64 |

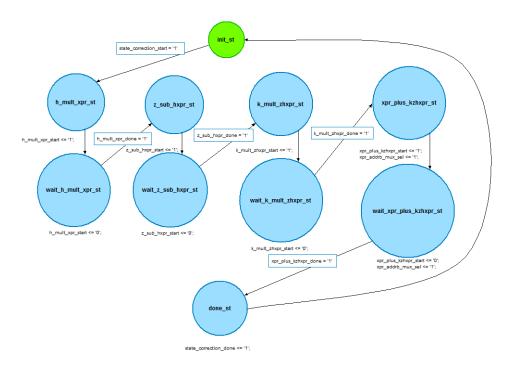

| 8.1.  | Top-level del módulo Correction                                                                                             | 69  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 8.2.  | Diagrama de estados del módulo $i\_correction\_fsm$                                                                         | 71  |

| 8.3.  | Diagrama de bloques del módulo $i\_gain\_local$                                                                             | 74  |

| 8.4.  | $Top$ -level del módulo $i\_state\_correction$                                                                              | 76  |

| 8.5.  | Diagrama de estados del módulo $i\_state\_correction\_fsm$                                                                  | 76  |

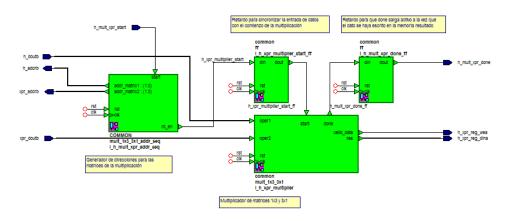

| 8.6.  | Diagrama de bloques del módulo $i\_h\_mult\_xpr$                                                                            | 78  |

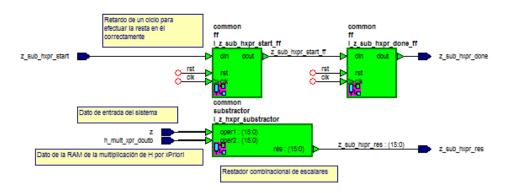

| 8.7.  | Diagrama de bloques del módulo $i\_z\_sub\_hxpr$                                                                            | 79  |

| 8.8.  | Diagrama de bloques del módulo $i\_xpr\_plus\_kzhxpr$                                                                       | 80  |

| 8.9.  | $Top$ -level del módulo $i\_covariance\_correction$                                                                         | 81  |

| 8.10. | $\label{linear_covariance_correction_fsm} \mbox{ Diagrama de estados de } i\_covariance\_correction\_fsm \ \ . \ . \ . \ .$ | 82  |

| 8.11. | Diagrama de bloques del módulo $i\_i\_sub\_kh$                                                                              | 84  |

| 8.12. | Diagrama de bloques del módulo $i\_ikh\_mult\_ppr$                                                                          | 84  |

| 8.13. | Diagrama de bloques del módulo $i\_xpo\_local$                                                                              | 86  |

| 9.1.  | Simulación con diferentes relaciones $Q/R$                                                                                  | 88  |

|       | Resultados de las simulaciones con diferentes pacientes                                                                     | 90  |

| 10.1. | Diagrama del camino crítico del FK                                                                                          | 94  |

| A.1.  | Formato $Q_{m.n}$                                                                                                           | 106 |

| A.2.  | Fórmulas para operar con notación ${\cal Q}$ manteniendo el deno-                                                           |     |

|       | minador constante                                                                                                           | 107 |

## Índice de Tablas

| 3.1.  | Variables del FK particularizado                                                  | 15 |

|-------|-----------------------------------------------------------------------------------|----|

| 3.2.  | Nomenclatura utilizada para referirse a las variables del filtro                  | 16 |

| 3.3.  | Convenio de representación                                                        | 16 |

| 4.1.  | Interfaz del FK                                                                   | 20 |

| 4.2.  | Entradas y salidas de los distintos módulos                                       | 23 |

| 4.3.  | Datos constantes                                                                  | 24 |

| 4.4.  | FIFOs instanciadas en el top-level                                                | 25 |

| 4.5.  | Tabla con las señales del módulo de escritura de FIFOs                            | 27 |

| 4.6.  | Tabla con las señales del módulo de lectura de FIFOs                              | 28 |

| 5.1.  | Tabla de traducción de $\mathbf{mult}_{3x1}_{1x3}_{\mathbf{addr}_{\mathbf{seq}}}$ | 32 |

| 5.2.  | Estados de la FSM del sumador                                                     | 33 |

| 5.3.  | Estados de la FSM del restador                                                    | 34 |

| 5.4.  | Estados de la FSM del multiplicador                                               | 36 |

| 6.1.  | Interfaz del módulo Prediction                                                    | 42 |

| 6.2.  | Instancias de memorias usadas en el módulo $i\_calc\_x$                           | 44 |

| 6.3.  | Estados de la unidad de control del módulo $i\_calc\_x$                           | 46 |

| 6.4.  | Elementos del módulo $i\_mult\_ax$                                                | 48 |

| 6.5.  | Instancias de memorias usadas en el módulo $i\_\mathit{calc}\_p$                  | 50 |

| 6.6.  | Estados de la unidad de control del módulo $i\_calc\_p$                           | 51 |

| 6.7.  | Elementos particularizados para el módulo $i\_mult1$                              | 53 |

| 6.8.  | Elementos particularizados para el módulo $i\_mult2$                              | 54 |

| 6.9.  | Elementos particularizados para el módulo $i\_add$                                | 55 |

| 6.10. | Tablas de verdad para el acceso a datos de diferentes operaciones                 | 55 |

| 7.1.  | Interfaz del módulo Gain                                                          | 57 |

| 7.2.  | Elementos a nivel top del módulo Gain                                             | 59 |

| 7.3.  | Instancias de memorias usadas en el módulo Gain                                   | 60 |

| 7.4.  | Estados de la unidad de control del módulo GAIN                                   | 60 |

| 7.5.  | Interfaz del módulo $i\_mult\_p\_ht$                                              | 63 |

XXII ÍNDICE DE TABLAS

| 7.6.  | Elementos particularizados para el módulo $i\_mult\_p\_ht$                | 64 |

|-------|---------------------------------------------------------------------------|----|

| 7.7.  | Interfaz del módulo $i\_mult\_hpht\_r$                                    | 65 |

| 7.8.  | Elementos del módulo $i\_mult\_hpht\_r$                                   | 65 |

| 7.9.  | Elementos de la división                                                  | 66 |

| 8.1.  | Interfaz del módulo Correction                                            | 68 |

| 8.2.  | Memorias utilizadas en el módulo Correction                               | 70 |

| 8.3.  | Estados de la unidad de control maestra del módulo Correc-                |    |

|       | TION                                                                      | 72 |

| 8.4.  | Módulos lectores de FIFO usados en Correction                             | 74 |

| 8.5.  | Interfaz del módulo $i\_gain\_local$                                      | 75 |

| 8.6.  | Estados de la unidad de control del módulo <i>i_state_correction</i>      | 77 |

| 8.7.  | Elementos del módulo $i_h_mult_xpr$                                       | 78 |

| 8.8.  | Elementos del módulo $i\_z\_sub\_hxpr$                                    | 79 |

| 8.9.  | Elementos del módulo $i\_xpr\_plus\_kzhxpr$                               | 80 |

| 8.10. | . Estados de la unidad de control de $i\_covariance\_correction$ .        | 82 |

|       | . Elementos del módulo $i$ $i$ $sub$ $kh$ $\dots$ $\dots$ $\dots$ $\dots$ | 85 |

| 8.12. | . Elementos del módulo $i\_ikh\_mult\_ppr$                                | 85 |

|       | . Módulos escritores en FIFO usados en CORRECTION                         | 86 |

|       | . Interfaz del módulo $i\_xpo\_local$                                     | 86 |

| 10.1. | . Módulos utilizados en la síntesis del proyecto                          | 92 |

# Parte I Estado del arte

### Capítulo 1

## Motivaciones del trabajo

La Diabetes Mellitus tipo 1 (DM1) es una enfermedad crónica autoinmune caracterizada por la destrucción de las células beta del páncreas, lo que le imposibilita producir insulina. Los pacientes con esta enfermedad no tienen la capacidad de generar suficiente insulina para llevar la glucosa del torrente sanguíneo a las células. Esto da lugar a un aumento de la glucosa en sangre (GS). Esta situación se conoce como hiperglucemia, y puede provocar problemas sanguíneos deteriorando la hemoglobina o los vasos sanguíneos. Si no se trata a tiempo, los efectos a largo plazo sobre el organismo pueden llevar al paciente a un estado de coma o incluso provocar su muerte.

Para poder llevar una vida normal, los pacientes de DM1 necesitan administrarse insulina subcutánea de por vida para suplir su déficit y evitar la hiperglucemia. Por otro lado, un exceso de insulina puede dar lugar a una situación de hipoglucemia, donde los niveles de GS son muy bajos, que es asimismo peligroso. El control glucémico es un punto crítico en este tipo de pacientes, que deben encontrar un punto de balance entre ambos extremos.

Para obtener el control glucémico autónomo es necesario que el paciente mida de forma regular su nivel de GS. Esto se puede hacer utilizando Monitores Continuos de Glucosa (MCG). Estos dispositivos no miden la GS directamente, sino que trabajan con la glucosa intersticial (GI), es decir, la que se encuentra en el espacio intercelular, siendo menos intrusivos para el paciente. Los MCG permiten medir la GI del paciente a intervalos de tiempo regulares, del orden de minutos.

El MCG por sí solo no basta para llevar a cabo un buen control glucémico. Necesita trabajar conjuntamente con un algoritmo que sea capaz de anticiparse al desarrollo del estado del paciente. Debe ser capaz de realizar predicciones con los datos proporcionados por dicho monitor. Una bomba de insulina proporciona esta sustancia al paciente según lo considere necesario el MCG. Juntos, estos elementos formarían un sistema conocido como Páncreas Artificial (PA).

Sin embargo el PA aún no se ha desarrollado plenamente, presentando

todavía ciertos problemas y dificultades. A continuación se listan una serie de problemas relacionados con los MCG:

- El sensor de glucosa que llevan incorporado introduce ruidos asociados a la medición. Además, se degradan progresivamente a lo largo de su vida útil. Esto dificulta la interpretación de los datos obtenidos y genera la necesidad de procesarlos primero.

- La glucosa se distribuye por el organismo a través del torrente sanguíneo y, antes de llegar a las células pasa por el fluido intersticial, que es donde el MCG efectúa las medidas para ser lo menos invasivo posible para el paciente. Debido a que el transporte de la glucosa de un medio a otro no es instantáneo el valor de la GI presenta cierto retraso frente al valor de la GS, por lo que los valores recogidos por el sensor no son los correspondientes a la GS del paciente en ese momento.

- El MCG necesita una calibración frecuente. Para ello se usa como referencia un muestreo de la GC del propio paciente.

- Es necesario ajustar de forma personalizada los parámetros de los filtros incluidos en el MCG para adaptarlos a las características individuales de cada paciente. Además, para un mismo paciente, factores como la edad, la alimentación, los hábitos de salud y la actividad diaria hacen que varíe el comportamiento de la glucosa en su organismo.

Una solución propuesta actualmente para estos problemas es la utilización de filtros Kalman. Éstos hacen uso de algoritmos recursivos que permiten identificar el estado oculto de un sistema utilizando medidas indirectas del mismo, al mismo tiempo que predicen su comportamiento futuro y eliminan el ruido de la señal. Las equivalencias con el monitor de glucosa son:

- El estado oculto del sistema es la glucosa en sangre, ya que se quiere medir sin actuar directamente sobre ella.

- La glucosa intersticial será la medida indirecta para identificar la GS debido a la relación que tiene con la misma.

El principal problema de esta propuesta es que la implementación de este tipo de filtros se hace mediante software. De esta manera, no pueden trabajar con otros datos que no estén procesados y tratados en primer lugar por el sensor. A causa de esto, los problemas listados anteriormente pueden verse agravados y el filtro no puede mostrar todo su potencial.

Para ofrecer una solución viable y factible a los problemas de los MCG existentes y de las implementaciones software del filtro Kalman, en este proyecto se implementa sobre una FPGA un filtro Kalman de tres estados (glucosa, velocidad de variación de la glucosa y aceleración de la velocidad de

dicha variación). Éste podrá utilizar como entrada las medidas reales de GI proporcionadas por un MCG sin que estén adulteradas por el tratamiento previo de los filtros digitales hardware de los sensores.

### Capítulo 2

### Teoría del filtro Kalman

El filtro de Kalman es un algoritmo propuesto por Rudolf E. Kalman en 1960 como solución recursiva al problema del filtrado de datos lineales discretos. Desde su introducción, debido a su robustez y simplicidad, ha sido usado en muchos ámbitos como en predicciones financieras, rastreo de misiles o navegación autónoma y asistida.

Está formado por un conjunto de ecuaciones matemáticas. Su objetivo es estimar de manera óptima el estado oculto de un sistema a partir de medidas indirectas del mismo.

El filtro de Kalman es útil para el filtrado de ruidos blancos y gausianos. Los ruidos blancos son aquellos cuyo valor no está correlacionado en el tiempo. Los ruidos gausianos son aquellos cuya amplitud en un instante de tiempo sigue una distribución de Gauss.

#### Existen dos tipos de FK:

- Discreto: Las ecuaciones de los modelos de proceso y de medición son lineales.

- Extendido: Las ecuaciones de los modelos de proceso y/o medición no son lineales.

En este trabajo se implementa el FK discreto, bajo la suposición de que las ecuaciones del modelo de la glucosa son lineales. Como modelo general se han utilizado las ecuaciones del Filtro de Kalman discreto propuestas por Welch y Bishop (2001). Toda la terminología del trabajo se ha adaptado a la nomenclatura de dicho artículo.

## 2.1. Ecuaciones generales para el filtro de Kalman discreto

#### 2.1.1. Ecuaciones de los modelos de proceso y medición

Es importante fijar estos modelos para la extracción posterior de las ecuaciones del filtro.

■ La ecuación del modelo del *proceso* es

$$x_k = Ax_{k-1} + Bu_k + w_{k-1} (2.1)$$

donde:

- $x_k$  es el vector del estado del proceso en el instante actual (k).

- $x_{k-1}$  es el vector del estado del proceso en el instante anterior (k-1).

- A es la matriz que relaciona el estado anterior con el estado actual (k).

- B es la matriz que relaciona el estado actual con la entrada de control.

- $u_k$  es una entrada de control en el instante actual (k).

- $w_{k-1}$  es el ruido asociado al proceso en el instante anterior (k-1).

- lacktriangle La ecuación del modelo de medición es

$$z_k = Hx_k + v_k \tag{2.2}$$

donde:

- $z_k$  es la medición en el instante actual (k).

- ullet H es la matriz que relaciona la medición con el estado actual.

- $v_k$  es el ruido asociado a la medición en el instante actual (k).

Las variables v y w representan ruidos del sistema. Estas señales se modelan como ruido blanco gausiano aditivo y siguen distribuciones normales de la siguiente forma:

$$p(w) \sim N(0, Q)$$

$$p(v) \sim N(0, R)$$

Los parámetros Q y R representan las covarianzas de dichos ruidos. Q es la covarianza del ruido del proceso mientras que R es la covarianza del ruido de la medición. En la práctica, estas variables pueden cambiar a lo largo del tiempo pero en este proyecto se asumirá que son constantes.

#### 2.1.2. Ecuaciones del Filtro de Kalman

El algoritmo consta de dos etapas: una de predicción, en la que proporciona una estimación del estado del sistema previa a la llegada de la medida, y otra de corrección, en la que utiliza la medición tomada por el sensor para corregir el estado del sistema y mejorar las predicciones futuras. Esto hace que las ecuaciones del FK se dividan en dos subconjuntos.

Ecuaciones de la etapa de predicción: estima el valor del estado en un instante futuro basándose en el estado corregido con la ultima medición tomada.

$$\hat{x_k} = A\hat{x}_{k-1} + Bu_k \tag{2.3}$$

donde:

- $\hat{x}_k^-$  representa el estado a priori, estimado antes de la medición.

- $\hat{x}_{k-1}$  representa el estado corregido *a posteriori*, calculado después de la medición.

- A, B y u representan los mismos parámetros que en el modelo del proceso.

у

$$P_{k}^{-} = AP_{k-1}A^{T} + Q (2.4)$$

donde

- $P_k^-$  es una medida de la precisión de la estimación del estado, también llamada covarianza del error de estimación. En este caso, la covarianza del error de estimación *a priori*, calculada en el instante actual (k).

- $P_{k-1}$  representa la covarianza del error *a posteriori*, calculada en el instante anterior (k-1).

- $\bullet\,$  Q representa la matriz de covarianza del ruido del proceso.

- A representa el mismo parámetro que en el modelo del proceso.

- Ecuaciones de la etapa de corrección: utilizan la medición y los datos a priori para calcular los valores a posteriori.

$$K_k = P_k^- H^T (H P_k^- H^T + R)^{-1}$$

(2.5)

donde:

- $K_k$  representa la ganancia de Kalman.

- $P_k^-$  representa la covarianza del error de estimación a priori.

- H es la misma matriz descrita en el modelo de medición.

- R es la covarianza del ruido de la medición.

$$\hat{x}_k = \hat{x}_k + K_k(z_k - H\hat{x}_k) \tag{2.6}$$

donde:

- $\hat{x}_k$  representa el estado a posteriori.

- $\hat{x}_{k}^{-}$  representa el estado a priori.

- $K_k$  representa la ganancia de Kalman.

- $\bullet$   $z_k$  representa la medida real tomada.

У

$$P_k = (I - K_k H) P_k^{\scriptscriptstyle -} \tag{2.7}$$

donde:

- $P_k$  representa la covarianza del error de estimación a posteriori.

- I es la matriz identidad.

- $K_k$  representa la ganancia de Kalman.

- ullet H es la misma matriz descrita en el modelo de medición.

- $P_k^-$  representa la covarianza del error de estimación a priori.

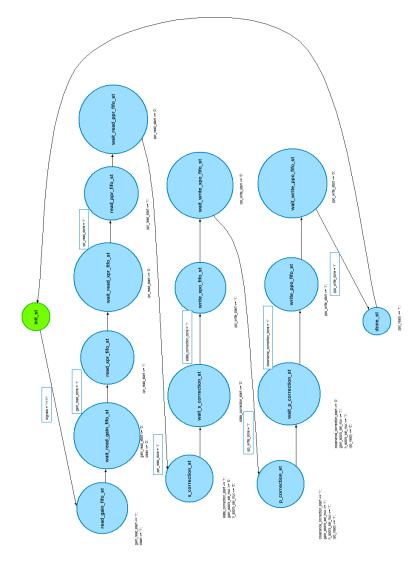

#### 2.1.3. Algoritmo

El filtro de Kalman sigue una dinámica del tipo predicción-corrección, en la que se proyecta el estado estimado para posteriormente corregirse con la medida real. El filtro de Kalman se describe por las ecuaciones mostradas en la figura 2.1, extraída de Welch y Bishop (2001).

Figura 2.1: Sistema de predicción-corrección con las ecuaciones de cada etapa

El algoritmo comienza con unas estimaciones iniciales que sirven para que el sistema tenga unos datos con los que poder empezar a funcionar. A partir de ahí:

#### ■ Predicción:

- Cálculo del estado del sistema x a priori a partir del estado a posteriori y la matriz constante A.

- Cálculo de la covarianza del error de estimación P a priori, a partir de la misma a posteriori, la matriz constante A y la matriz de covarianza del ruido del proceso Q.

#### ■ Corrección:

- Comienza con el cálculo de la ganancia una vez se tenga calculada la covarianza del error *a priori*, necesaria para calcular tanto el estado como la covarianza del error *a posteriori*.

- Se incorpora la medición y, junto con la ganancia, se calcula el estado *a posteriori*.

- Cálculo de la covarianza del error *a posteriori* a partir de la predicción y la ganancia.

### Capítulo 3

## Modelo del Filtro de Kalman propuesto por Palerm

Como se ha indicado en la sección 2.1.1, es importante fijar los modelos de proceso y de medición. Estos modelos son los que determinan si el filtro será discreto o extendido, las dimensiones de todas las matrices, así como los valores de las matrices constantes A y H. En este proyecto se han usado como referencia los artículos Palerm et al. (2005) y Palerm y Bequette (2007).

Según estos artículos, el modelo de proceso queda definido por:

$$g_{k+1} = g_k + d_k$$

$$d_{k+1} = d_k + f_k$$

$$f_{k+1} = f_k + w_k$$

donde

- $\bullet$  g es la glucosa intersticial

- lacktriangle de la velocidad de variación de la glucosa intersticial, es decir, la derivada primera de g

- f es la velocidad de variación de d, por tanto la derivada primera de d

o, lo que es lo mismo, la derivada segunda de g

- $\bullet$  w es el ruido blanco gaussiano aditivo del proceso, con covarianza Q

El modelo de medición descrito en los mismos artículos es:

$$y_k = g_k + v_k$$

donde

$\bullet$  y es el valor medido

- $\bullet$  g es la glucosa intersticial

- ullet v es el ruido blanco gaussiano aditivo de la medición, con covarianza R

Los subíndices k y k+1 indican el instante de tiempo actual y el instante de tiempo siguiente, respectivamente.

La primera información que extraemos de estos modelos es que ambos son lineales, por lo tanto el filtro que se tiene que implementar es discreto y no extendido. A continuación representamos estos modelos en forma matricial:

$$\begin{bmatrix} g_{k+1} \\ d_{k+1} \\ f_{k+1} \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} g_k \\ d_k \\ f_k \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ 1 \end{bmatrix} w_k$$

$$y_k = \begin{bmatrix} 1 & 0 & 0 \end{bmatrix} \begin{bmatrix} g_k \\ d_k \\ f_k \end{bmatrix} + v_k$$

Se puede observar que en estas expresiones no aparece el término de Bishop  $Bu_k$ . Esto se debe a que el modelo de Bishop es un modelo general y supone que existe una entrada de control  $(u_k)$ . Sin embargo, en los filtros aplicados al control de glucosa no se utiliza dicha entrada, por lo tanto el término  $Bu_k$  desaparece de la expresión. Si se ponen estas ecuaciones en forma compacta, adquieren la siguiente forma

$$x_k = Ax_{k-1} + w_k$$

$$z_k = Hx_k + v_k$$

, que concuerda con las expresiones de Bishop, salvo por el término correspondiente a la entrada de control que se ha eliminado.

Por consiguiente tenemos que x es una matriz de 3x1 que contiene los 3 estados del proceso:

$$x_k = \begin{bmatrix} g_k \\ d_k \\ f_k \end{bmatrix}$$

A es una matriz 3x3:

$$A = \begin{bmatrix} 1 & 1 & 0 \\ 0 & 1 & 1 \\ 0 & 0 & 1 \end{bmatrix}$$

H es una matriz 1x3:

$$H = \begin{bmatrix} 1 & 0 & 0 \end{bmatrix}$$

| Variable       | Descripción                     | Dimensiones      | Tamaño    |

|----------------|---------------------------------|------------------|-----------|

| $\overline{x}$ | Vector de estados               | nx1              | 3x1       |

| A              | Matriz que relaciona el estado  | $n \mathbf{x} n$ | 3x3       |

|                | actual con el anterior          |                  |           |

| B              | Matriz que relaciona el control | -                | no se usa |

|                | con el estado                   |                  |           |

| H              | Matriz que relaciona la medi-   | mxn              | 1x3       |

|                | ción con el estado              |                  |           |

| z              | Medición                        | mx1              | 1x1       |

| K              | Ganancia de Kalman              | nxm              | 3x1       |

| Q              | Covarianza del ruido del pro-   | $n \mathbf{x} n$ | 3x3       |

|                | ceso                            |                  |           |

| P              | Covarianza del error asociada   | $n \mathbf{x} n$ | 3x3       |

|                | a la estimación                 |                  |           |

| R              | Covarianza del ruido de la me-  | mx $m$           | 1x1       |

|                | dición                          |                  |           |

Tabla 3.1: Variables del FK particularizado

En la tabla 3.1 se particularizan las dimensiones de los elementos del FK propuesto por Palerm.

Volviendo al modelo genérico de Bishop que se muestra en la figura 2.1 pero aplicando el modelo particularizado de Palerm, las ecuaciones del sistema nos quedarían como en la figura 3.1. Nótese que la única diferencia es la ausencia de los parámetros  $Bu_k$ , puesto que en este sistema no se usan las entradas de control.

Figura 3.1: Sistema de predicción-corrección con las ecuaciones del modelo de Palerm

En el resto del documento, para hablar de las variables de estas ecuaciones, se va a usar la nomenclatura que se muestra en la tabla 3.2. Además, en la tabla 3.3se definen los convenios de estilo que se han utilizado para representar diferentes elementos en el documento.

| Variable         | Nombre | Descripción                                                   |

|------------------|--------|---------------------------------------------------------------|

| $\overline{A}$   | A      | Constante $A$ , matriz de dimensiones $3x3$ .                 |

| $A^T$            | $A^T$  | Traspuesta de $A$ , matriz de dimensiones $3x3$ .             |

| H                | H      | Constante $H$ , matriz de dimensiones $1x3$ .                 |

| $H^T$            | $H^T$  | Traspuesta de $H$ , matriz de dimensiones $3x1$ .             |

| I                | I      | Matriz <i>identidad</i> , de dimensiones 3x3.                 |

| $K_k$            | K      | Ganancia de Kalman, matriz de 3x1.                            |

| $\hat{x}_k^-$    | XPR    | Estado estimado a priori, matriz de dimensiones 3x1.          |

| $\hat{x}_k$      | XPO    | Estado corregido a posteriori, matriz de dimensiones 3x1.     |

| $P_k^{\text{-}}$ | PPR    | Covarianza del error a priori, matriz de dimensiones 3x3.     |

| $P_k^n$          | PPO    | Covarianza del error a posteriori, matriz de dimensiones 3x3. |

| Q                | Q      | Covarianza del ruido del proceso, matriz de dimensiones 3x3.  |

| R                | R      | Covarianza del ruido de la medida, escalar.                   |

| z                | z      | Medida que entra al sistema, escalar.                         |

Tabla 3.2: Nomenclatura utilizada para referirse a las variables del filtro

| Elemento                       | Estilo             | Ejemplo                           |

|--------------------------------|--------------------|-----------------------------------|

| módulos principales            | SMALL CAPS         | GAIN                              |

| ${ m entidades}$               | $\mathbf{negrita}$ | ${ m fifo\_write}$                |

| instancias de una entidad      | cursiva            | $i\_\ calc\_\ x$                  |

| recepción de señal en una FSM  | $\leftarrow$       | $done\_mul \leftarrow 1$          |

| asignación de señal en una FSM | $\rightarrow$      | $start\_fifo\_read \rightarrow 1$ |

Tabla 3.3: Convenio de representación

# Parte II Implementación

# Capítulo 4

# Módulo Filtro de Kalman

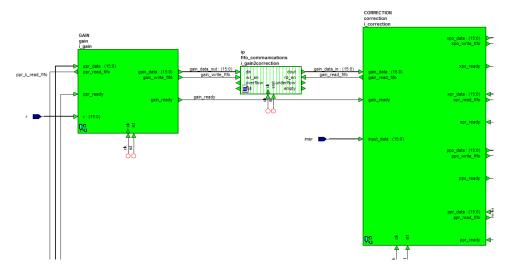

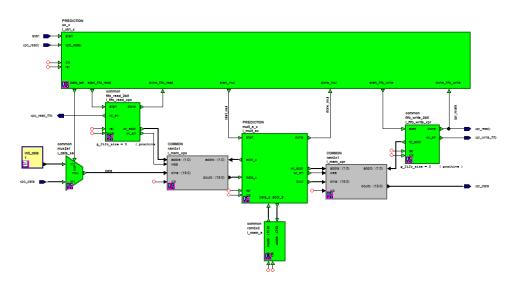

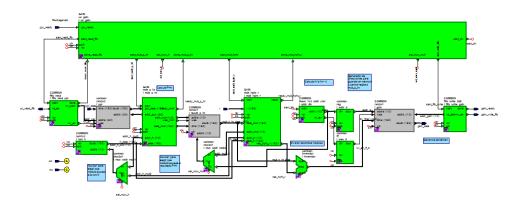

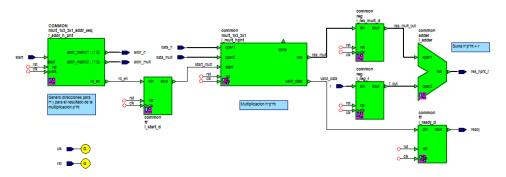

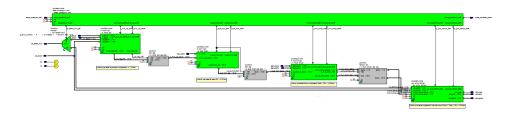

Como se puede observar en la figura 4.1, el módulo top-level del diseño se descompone en tres submódulos principales, y en cada uno de ellos se implementa una parte del sistema de ecuaciones vistas en el capítulo 3. En la tabla 4.1 se puede consultar su interfaz.

En la implementación de estos módulos se han utilizado una serie de elementos comunes a los que se dedica un capítulo, puesto que es necesario explicarlos para entender mejor la implementación de los otros módulos. En los siguientes capítulos se procede a explicar con mayor profundidad cada uno de estos módulos:

- Módulos Comunes: Elementos comunes instanciados en los módulos principales. (Capítulo 5).

- Prediction: Implementa las ecuaciones 2.3 y 2.4. (Capítulo 6).

- GAIN: Implementa la ecuación 2.5. (Capítulo 7).

- Correction: Implementa las ecuaciones 2.6 y 2.7. (Capítulo 8).

Por otro lado, en las distintas secciones de este capítulo se va a explicar:

- Representación de los datos: es importante saber cómo se representan los datos para operar con ellos correctamente. (Sección 4.1)

- El funcionamiento general del filtro: antes de entrar a ver el funcionamiento interno de cada submódulo, es conveniente entender cómo interaccionan éstos a alto nivel. (Sección 4.2)

- Datos intercambiados y constantes: qué datos se intercambian o usan los módulos. (Sección 4.3)

- Las FIFOs: Se han utilizado para desacoplar el intercambio de información entre los módulos principales. (Sección 4.4)

■ El protocolo de comunicación: Para que los módulos tuvieran un comportamiento homogéneo a la hora de transmitir sus resultados, se diseñó un protocolo para la comunicación entre ellos. (Sección 4.5)

| Nombre                       | Tamaño  | Sentido                 | Comentario                          |

|------------------------------|---------|-------------------------|-------------------------------------|

| imsr                         | 16 bits | entrada                 | Medición recibida del monitor con-  |

|                              |         |                         | tinuo de glucosa.                   |

| $\operatorname{imsr\_ready}$ | 1 bit   | entrada                 | Indica que imsr está listo para ser |

|                              |         |                         | ${ m utilizado.}$                   |

| r                            | 16 bits | entrada                 | Covarianza asociada a la medida     |

|                              |         |                         | (matriz  1x1 R).                    |

| $q\_addr$                    | 4 bits  | entrada                 | Proporciona la dirección de lectura |

|                              |         |                         | de Q.                               |

| $q\_data$                    | 16 bits | entrada                 | Entrada de datos de la memoria ex-  |

|                              |         |                         | terna $Q$ .                         |

| $\operatorname{start}$       | 1 bit   | entrada                 | Inicio global del sistema.          |

| ${ m xpo\_data\_out}$        | 16 bits | $\operatorname{salida}$ | Salida del resultado del filtro.    |

| ${ m xpo\_write\_fifo}$      | 1 bit   | $\operatorname{salida}$ | Notifica la salida del resultado.   |

Tabla 4.1: Interfaz del FK

# 4.1. Representación de los datos

Las medidas generadas por el sensor tienen que poder ser interpretadas por el filtro. Para ello se convierten a un formato digital que el sistema pueda manejar. El sistema trabaja con vectores de 16 bits. Para la representación que se la coma fija, ya que es más sencilla de implementar que la coma flotante, y además no es necesaria la potencia y precisión de esta última representación.

Para concretar el formato es necesario tener en cuenta los valores más altos que se necesitan representar. Los valores entre los que suele oscilar la glucemia están comprendidos en el intervalo de 100 a 300 mg/dl. Para representar estos valores es necesaria como mínimo una parte entera de 9 bits, con la que se puedan representar  $2^9 = 512$  valores.

Contando con el bit de signo y el probable desbordamiento que se pueda producir en los cálculos, se ha decidido utilizar una parte entera de 12 bits y una parte decimal de 4 (en notación Q corresponde a Q12,4). Se sacrifica precisión por un mayor rango de valores, pero en este caso 4 bits proporcionan una precisión suficiente.

La representación en coma fija se explica más en detalle en el apéndice A.

Figura 4.1: Módulo Filtro de Kalman a nivel top

### 4.2. Funcionamiento general

#### Sistema cíclico

El Filtro de Kalman es un sistema recursivo, que se retroalimenta para conseguir estimar los estados de forma óptima. Esto implica la existencia de un ciclo en el cual cada módulo, en una iteración dada, realiza las siguientes tareas básicas:

- 1. Lee el dato proporcionado por el módulo emisor.

- 2. Procesa el dato.

- 3. Pasa a ser módulo emisor y proporciona el dato al módulo receptor.

Este ciclo se repite de forma indefinida mientras el sistema no sea reseteado.

#### Inicio del sistema

El hecho de que el sistema sea cíclico genera un problema a la hora de iniciar los cálculos, puesto que no existe ningún módulo emisor que genere datos iniciales del sistema. Por ello, es necesario que en la primera iteración se carguen estos datos iniciales con los que realizar los cálculos. Considerando esto como una fase de inicialización, el sistema entra en el ciclo de filtrado inmediatamente después. De esta forma:

- 1. El sistema empieza a funcionar cuando se activa la señal start.

- 2. Esta señal activa el módulo Prediction, que es el encargado de llevar a cabo dicha fase de inicialización del sistema.

- 3. Una vez que el módulo Prediction termina los cálculos con los valores iniciales, los pasa a los módulos receptores.

- 4. Las siguientes iteraciones siguen según los puntos explicados en la sección 4.2.

### 4.3. Datos intercambiados y constantes

#### Datos salientes y entrantes

En la tabla 4.2 se detalla, para cada módulo, la información de entrada y de salida, sus dimensiones, su origen o destino y el nombre que se le ha dado en la interfaz del módulo.

|            | Observaciones | Estado <i>a posteriori</i> Covarianza P <i>a posteriori</i> Dato generado por adaptación | Observaciones | Estado <i>a priori</i><br>Covarianza P <i>a priori</i> |      | Observaciones | Covarianza P <i>a priori</i><br>Dato generado por adaptación | Observaciones | Ganancia   |            | Observaciones | Estado <i>a priori</i><br>Ganancia | Viene de una medida exterior Covarianza P $a\ priori$ | Observaciones | Estado a posteriori | Covarianza r <i>a posteriori</i> |

|------------|---------------|------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------|------|---------------|--------------------------------------------------------------|---------------|------------|------------|---------------|------------------------------------|-------------------------------------------------------|---------------|---------------------|----------------------------------|

| ION        | Nombre        | xpo_data<br>ppo_data<br>q data                                                           | Nombre        | xpr_data<br>ppr_data                                   |      | Nombre        | ppr_data<br>r                                                | Nombre        | gain_data  | NOI        | Nombre        | xpr_data<br>gain_data              | imsr<br>ppr_data                                      | Nombre        | xpo_data            | ppo_data                         |

| Prediction | Origen        | CORRECTION CORRECTION Exterior                                                           | Destino       | CORRECTION CORRECTION y GAIN                           | GAIN | Origen        | Prediction<br>Exterior                                       | Destino       | CORRECTION | CORRECTION | Origen        | Prediction<br>Gain                 | Lectura<br>Prediction                                 | Destino       | PREDICTION          | FREDICTION                       |

|            | Dimensiones   | 3x1<br>3x3<br>3x3                                                                        | Dimensiones   | 3x1<br>3x3                                             |      | Dimensiones   | 3x3<br>1x1                                                   | Dimensiones   | 3x1        |            | Dimensiones   | 3x1<br>3x1                         | escalar<br>3x3                                        | Dimensiones   | 3x1                 | охо                              |

|            |               | XPO<br>PPO                                                                               |               | XPR<br>PPR                                             |      |               | $\frac{\mathrm{PPR}}{R}$                                     |               | K          |            |               | XPR<br>K                           | $z \ \mathrm{PPR}$                                    |               | XPO                 |                                  |

|            |               | Entrada                                                                                  |               | sbils                                                  |      |               | absiti                                                       | EI            | sbils2     |            |               | rada                               | Ent                                                   |               | sbila               | βS                               |

Tabla 4.2: Entradas y salidas de los distintos módulos

#### Datos constantes

Además de los datos que intercambian los módulos entre sí o reciben desde el exterior, existen una serie de datos que son constantes, equivalentes a las matrices constantes de las ecuaciones del filtro. Estas constantes se han implementado mediante memorias ROM que se han instanciado dentro de cada módulo. En la tabla 4.3 se detallan sus tamaños y dónde se usan.

| Constante     | Dimensiones     | Uso                                     | Nombre matriz                 |

|---------------|-----------------|-----------------------------------------|-------------------------------|

| - А<br>Н<br>І | 3x3 $1x3$ $3x3$ | PREDICTION GAIN y CORRECTION CORRECTION | c_rom_a<br>c_rom_H<br>c_rom_I |

Tabla 4.3: Datos constantes

#### 4.4. FIFOs

Como se ha visto en el apartado anterior, los módulos principales tienen que intercambiar información entre sí. El mecanismo de intercambio de datos se basa en el uso de memorias FIFO. En la imagen 4.2 se muestra la interfaz de las mismas. Es importante hacer notar que en este diseño no se han utilizado los puertos overflow, full, underflow y empty, puesto que el protocolo elaborado en la sección 4.5 se encarga del control del flujo de datos.

Figura 4.2: Interfaz de las FIFOs utilizadas en el diseño

El tamaño de las FIFOs que se han utilizado es de 16 posiciones. Sin embargo los datos que se intercambian entre los módulos no llegan a tener tantos elementos, por lo que es importante saber cuántos elementos se van a pasar a través de la misma para definir correctamente el protocolo de intercambio de datos.

En el top-level del FK se han instanciado 6 FIFOs, cuyos nombres y el número de elementos que se intercambian a través de ellas se detallan en la tabla 4.4.

| Nombre                        | Nº elementos |

|-------------------------------|--------------|

| $i\_correction2prediction\_x$ | 3            |

| $i\_prediction2correction\_x$ | 3            |

| $i\_correction2prediction\_p$ | 9            |

| $i\_prediction2correction\_p$ | 9            |

| $i\_prediction2gain\_p$       | 9            |

| $i\_gain2correction$          | 3            |

Tabla 4.4: FIFOs instanciadas en el top-level

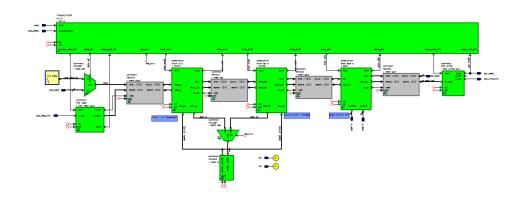

#### 4.5. Protocolo de comunicación

Una vez resuelto el problema del intercambio de datos mediante la incorporación de FIFOs al diseño, surgió la necesidad de coordinar los tres módulos para las escrituras y lecturas de las mismas. Llamaremos módulo emisor al que genera el dato y módulo receptor al que lo recibe. En el ejemplo de la figura 4.3 se puede apreciar que el módulo GAIN es el emisor de datos y Correction es el módulo receptor. El protocolo de comunicación es el siguiente:

- Cuando un módulo emisor ha terminado el cálculo de un dato, lo escribe en la FIFO.

- Una vez que ha concluido la escritura, activa una señal (gain\_ready en el ejemplo) durante un único ciclo de reloj para indicar al módulo receptor que el dato que necesita está disponible.

- Esta señal activa la lectura de la FIFO por el módulo receptor.

Figura 4.3: Protocolo de comunicación mediante FIFOs

#### Escritura de la FIFO

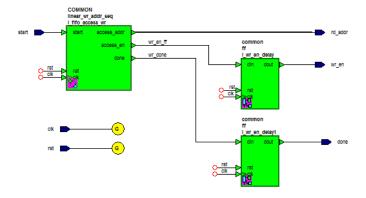

El módulo encargado de esta tarea es **fifo\_write**, cuyo diagrama de bloques de puede observar en la figura 4.4. El control lo realiza el módulo emisor. Se controla mediante una máquina de estados ( $i\_fifo\_access\_wr$ ) que tiene un estado inicial y un estado de espera de n ciclos, siendo n el número de datos que tiene que escribir (n=9 para matrices 3x3 y n=3 para matrices 3x1). Los flip-flops  $i\_wr\_en\_delay$  y  $i\_wr\_en\_delay1$  se utilizan para la correcta sincronización de este módulo con los módulos con los que interactúa.

En la tabla 4.5 se describen las señales necesarias para el control.

Figura 4.4: Módulo encargado de la escritura de las FIFOs

| Nombre       | Tamaño   | Sentido                 | Propósito                            |

|--------------|----------|-------------------------|--------------------------------------|

| start        | 1 bit    | entrada                 | Activa el proceso de escritura       |

| $_{ m done}$ | 1 bit    | $\operatorname{salida}$ | Fin del proceso de escritura         |

| $rd\_addr$   | 2/4 bits | $\operatorname{salida}$ | Dirección de la memoria RAM del dato |

|              |          |                         | que se va a escribir en la FIFO      |

| $wr_en$      | 1 bit    | salida                  | Habilita la escritura en la FIFO     |

Tabla 4.5: Tabla con las señales del módulo de escritura de FIFOs

El cronograma de la figura 4.5 muestra la secuencia de acciones que se llevan a cabo durante la escritura.

- El proceso de escritura comienza cuando se recibe la señal start.

- En el ciclo siguiente se empiezan a proporcionar direcciones para leer desde la RAM que se va a escribir en la FIFO.

- Un ciclo más tarde se habilita la escritura en FIFO. Esto es porque la RAM tarda un ciclo en proporcionar el dato pedido.

- Cuando se ha escrito el último dato, se activa la señal done.

Figura 4.5: Cronograma de la escritura de las FIFOs

#### Lectura de la FIFO

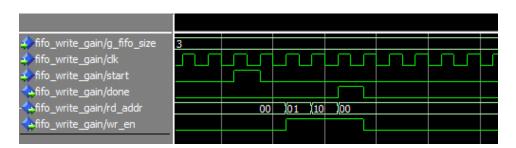

El módulo encargado de esta tarea es **fifo\_read**, cuyo diagrama de bloques se puede observar en la figura 4.6. El control lo realiza el módulo receptor. Se realiza mediante un estado inicial y un estado de espera de n ciclos, siendo n el número de datos que tiene que leer (n=9 para matrices 3x3 y n=3 para matrices 3x1). En la tabla 4.6 se describen las señales necesarias para el control.

| Nombre        | Tamaño         | Sentido           | Propósito                                                                                        |

|---------------|----------------|-------------------|--------------------------------------------------------------------------------------------------|

| start<br>done | 1 bit<br>1 bit | entrada<br>salida | Activa el proceso de lectura<br>Fin del proceso de lectura                                       |

| $rd_en$       | 1 bit          | salida            | Activa la FIFO para que proporcione los                                                          |

| wr_addr       | 2/4 bits       | salida            | datos que contiene Dirección de la memoria RAM sobre la que se almacena el dato leído de la FIFO |

| wr_en         | 1 bit          | salida            | Habilita la escritura en la memoria RAM                                                          |

Tabla 4.6: Tabla con las señales del módulo de lectura de FIFOs

Figura 4.6: Módulo encargado de la lectura de las FIFOs

En el cronograma de la figura 4.7 se puede observar la secuencia de acciones que se llevan a cabo durante la lectura.

- El proceso de lectura comienza cuando se activa la señal start.

- En el ciclo siguiente el módulo envía la habilitación de lectura a la FIFO.

- Un ciclo más tarde activa la escritura en la RAM y empieza a generar

direcciones. Esto se debe a que la FIFO tarda un ciclo en proporcionar el dato.

• Coincidiendo con la escritura en RAM el último dato, se activa la señal done para avisar de que se han leído todos los datos de la FIFO.

Figura 4.7: Cronograma de la lectura de las FIFOs

# Capítulo 5

# Módulos Comunes

Las tareas complejas de los módulos principales se pueden descomponer en tareas más simples. Éstas son realizadas por módulos más sencillos que se pueden reutilizar. En este capítulo se clasificarán y se detallarán por tipos dicho módulos.

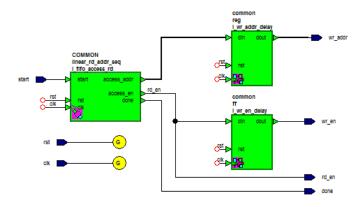

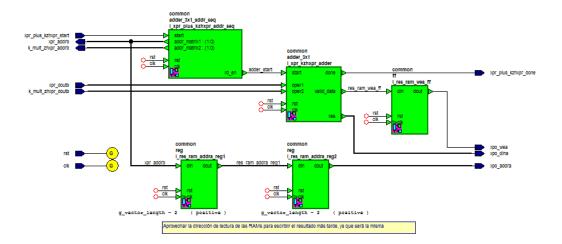

### 5.1. Generadores de direcciones

Las matrices del diseño se almacenan por filas en memorias RAM lineales. Para operar con ellas es necesario poder acceder en el orden correcto a sus componentes. Los módulos generadores de direcciones se encargan de esta tarea, proporcionando para cada operación las direcciones adecuadas para cada uno de los operandos. Para la escritura de resultados se usan otros generadores de direcciones que permiten la escritura lineal de resultados sobre las RAMs.

Estos son todos los módulos generadores de direcciones:

- Suma

- adder\_3x1\_addr\_seqadder 3x3 addr seq

- Resta

- sub 3x3 addr seq

- Multiplicación

- mult\_1x3\_3x1\_addr\_seq

mult\_3x1\_1x3\_addr\_seq

mult\_3x1\_scalar\_addr\_seq

mult\_3x3\_3x1\_addr\_seq

- mult addr seq (para dos matrices de dimensiones 3x3)

- mult addr seq trasp

- Escritura lineal

- linear 1x3 addr cntr

- linear 3x3 addr cntr

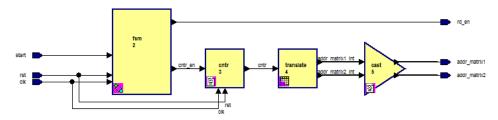

Para explicar estos módulos se ha tomado como ejemplo el secuenciador de la multiplicación de  $3x1_1x3$  dado que el diseño del resto de los secuenciadores es muy similar.

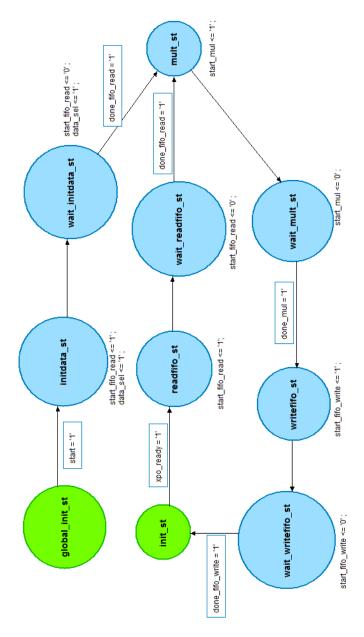

Figura 5.1: Ejemplo de módulo generador de direcciones

- La máquina de estados fsm activa una señal de capacitación para el contador que permanece activa un número de ciclos igual al número de elementos que hay que leer de la memoria. En este ejemplo la señal estará activa durante 9 ciclos.

- El contador *cntr* cuenta hasta 9 mientras esté habilitado.

- La tabla de traducción translate, implementada mediante una tabla de verdad, traduce cada número generado por el contador en las direcciones de las 2 memorias de las que se va a leer (en la tabla 5.1 se puede ver la traducción de este ejemplo). Esta forma nos permite tener una sola copia de las matrices constantes, ya que cambiando la tabla de traducción podemos leer una matriz de forma traspuesta.

- El módulo *cast* realiza una conversión de entero a vector.

| $\overline{\text{cntr}}$ | addr1 | addr2 | $\operatorname{cntr}$ | addr1 | addr2 |

|--------------------------|-------|-------|-----------------------|-------|-------|

| 0                        | 0     | 0     | 5                     | 1     | 2     |

| 1                        | 0     | 1     | 6                     | 2     | 0     |

| 2                        | 0     | 2     | 7                     | 2     | 1     |

| 3                        | 1     | 0     | 8                     | 2     | 2     |

| 4                        | 1     | 1     |                       |       |       |

Tabla 5.1: Tabla de traducción de mult 3x1 1x3 addr seq

# 5.2. Operadores

#### Suma de matrices

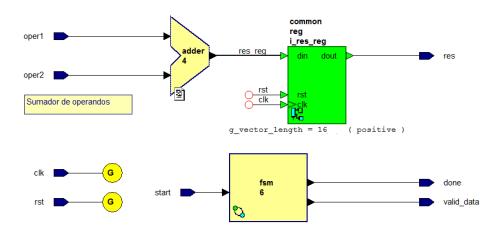

Estos módulos efectúan la suma de dos matrices componente a componente. Hay dos tipos de módulos sumadores:

- $\blacksquare$  adder 3x1

- $\blacksquare$  adder 3x3

Los sumadores de matrices se descomponen en un sumador, un registro para sincronizar el dato con la señal que indica que es válido y una máquina de estados (FSM). Su diagrama de bloques se puede ver en la figura 5.2. Los estados de la FSM se explican en la tabla 5.2.

| Estado                        | Acción                                                                   |

|-------------------------------|--------------------------------------------------------------------------|

| init_st                       | Espera que la señal de start $\leftarrow 1$ para empezar.                |

| $\operatorname{add}$ _st      | Espera durante tantos ciclos como sumas se deban efectuar                |

|                               | y activa valid_data $\rightarrow 1$ .                                    |

| $\mathrm{done} \_\mathrm{st}$ | Indica la conclusión de la suma y activa la señal done $\rightarrow 1$ . |

Tabla 5.2: Estados de la FSM del sumador

Figura 5.2: Módulo sumador 3x3

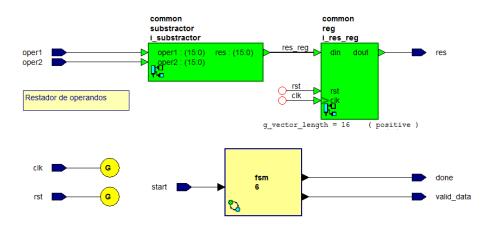

#### Resta de matrices

Al igual que la suma, la resta se efectúa elemento a elemento. Hay un módulo para esta operación:

### • $subs_3x3$

$Subs\_3x3$  lleva a cabo la resta entre dos matrices de tamaño 3x3. Para ello usa una instancia de  $substractor^1$  como restador, un registro para retardar el resultado un ciclo (para la sincronización del dato con la señal que indica que es válido) y una máquina de estados, similar a la de la suma (tabla 5.3), para controlar su funcionamiento.

| Estado                        | Acción                                                                   |

|-------------------------------|--------------------------------------------------------------------------|

| init_st                       | Espera que la señal de start $\leftarrow 1$ para empezar.                |

| $\mathrm{sub\_st}$            | Espera durante tantos ciclos como restas se deban efectuar               |

|                               | y activa valid_data $\rightarrow 1$ .                                    |

| $\mathrm{done} \_\mathrm{st}$ | Indica la conclusión de la resta y activa la señal done $\rightarrow$ 1. |

Tabla 5.3: Estados de la FSM del restador

En la figura 5.3 se puede observar el diagrama de bloques de este módulo.

Figura 5.3: Módulo restador 3x3

$<sup>^{1}</sup>$ **substractor** es un restador simple de escalares

5.2. Operadores 35

#### Multiplicación de matrices

Estos módulos realizan la multiplicación de una fila por una columna, es decir  $a_{11} * b_{11} + a_{12} * b_{21} + a_{13} * b_{31}$ . Debido a las peculiaridades de la multiplicación de matrices, es especialmente importante la generación de direcciones para leer en el orden adecuado las componentes de las matrices que se van a multiplicar. Es por ello que los multiplicadores están estrechamente vinculados a los generadores de direcciones. Existen las siguientes variantes, que se diferencian en el número de ciclos:

- mult 1x3 3x1

- mult 1x3 3x3

- mult 3x1 1x3

- mult 3x1 scalar

- mult 3x3 3x1

- mult 3x3 3x3

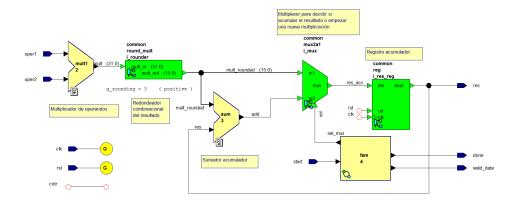

El diagrama de bloques de este módulo se puede observar en la figura 5.4.

Figura 5.4: Módulo multiplicador 3x3 con 3x3

- La señal start se debe recibir a la vez que los primeros datos a multiplicar  $(a_{11} * b_{11})$ . Tras multiplicarlos, se les aplica el redondeo (explicado más abajo) y se envían al registro acumulador seleccionando la primera entrada del multiplexor.

- De esta forma cuando la FSM pasa al siguiente estado ya tiene la primera multiplicación en el registro y se puede acumular al resultado de las siguientes (a  $a_{11} * b_{11}$  que ya estaba en el registro se le suma  $a_{12} * b_{21}$ ).

- En el estado de acumulación se selecciona la segunda entrada del multiplexor para dejar paso al resultado del sumador, que lleva acumulado el resultado anterior con el que acaba de salir del multiplicador  $(a_{11} * b_{11} + a_{12} * b_{21})$ . Esto se hace durante dos ciclos en este ejemplo.

- Al terminar se manda una señal para avisar de que el dato que sale es un resultado válido, puesto que cada elemento de la nueva matriz se almacena en la RAM nada más estar disponible. El registro acumulador se borra y se vuelve a empezar.

- En este ejemplo, este proceso se repite 9 veces. Al final se activa otra señal que indica la finalización de la multiplicación de las matrices.

La máquina de estados que controla el multiplicador tiene cuatro estados, detallados en la tabla 5.4. En el segundo estado de la tabla n establece el número de ciclos en función de los operandos que se tengan que acumular.

| Estado                    | Acción                                                           |

|---------------------------|------------------------------------------------------------------|

| init_st                   | Espera que la señal de start $\leftarrow 1$ para empezar.        |

| $\operatorname{mult\_st}$ | Espera $n$ ciclos y selecciona la entrada del mux para acumular. |

| $wr\_st$                  | Indica que el dato que llega es el resultado de la acumulación.  |

| $\_done\_st$              | Indica la conclusión de la multiplicación.                       |

Tabla 5.4: Estados de la FSM del multiplicador

Para que el resultado de la operación de multiplicación sea el correcto, se debe redondear debido a la aritmética en punto fijo<sup>2</sup>. Para ello se utiliza un módulo de redondeo, en el cual se suma un 1 al bit 4 debido a que es el bit más significativo de la parte que se quiere redondear. Después, se realiza un desplazamiento a la derecha de 4 bits. Por último, se restablece el signo del número inicial.

Poniendo un ejemplo, supóngase que se quieran multiplicar los números 3,6875 y 4,25. Su representación en notación  $Q_{12,4}$  es:

$$3,6875 = 0000000000111011 = 59_{(10)}$$

$4,25 = 0000000001000100 = 68_{(10)}$

Por lo tanto,

$$3,6875*4,25=15,671875$$

que corresponde a

<sup>&</sup>lt;sup>2</sup>Ver apendice A.

#

Nótese que el resultado binario tiene el doble de bits. Esto es porque al multiplicar dos vectores de 16 bits da como resultado uno de 32 bits.

Interpretándolo como números enteros, la multiplicación corresponde a

$$59 * 68 = 4012$$

El resultado de la multiplicación binaria no representa el resultado de los números reales. Para que corresponda es necesario realizar una serie de operaciones sobre aquél. Los pasos a realizar son:

1. El resultado anterior requiere ser redondeado. En este ejemplo se van a redondear 4 bits. Para ello se debe sumar un 1 al bit más significativo que se va a redondear (el cuarto en este caso).

$000000000000000000111110101100\\ +1000\\ \hline 0000000000000000000111110110100$

2. Se eliminan los 4 últimos bits haciendo un desplazamiento a la derecha.

####

3. Se mantiene el bit de signo y se extraen los 15 bits menos significativos.

$$15,6875 = 0000000011111011 = 251_{(10)}$$

El resultado ahora sí es el correcto, aunque se puede observar que no coincide exactamente con el resultado de la operación en números reales. Sin embargo 15,6875 es la representación más próxima y precisa que se puede hacer de 15,671875 en notación  $Q_{12,4}$ .

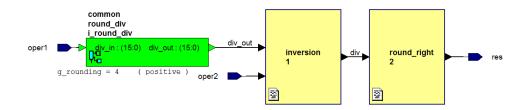

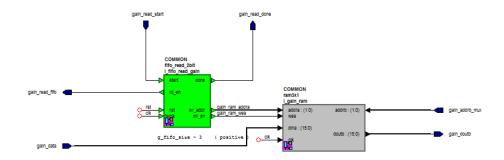

#### División o inversión

En el módulo Gain se debe efectuar una división de una matriz por otra. Para el caso particular que se ha dado en este proyecto, la matriz divisor tiene unas dimensiones de 1x1, es decir, es un escalar, por lo que el módulo **inversion** realiza una división simple de una matriz entre un escalar. En la figura 5.5 se puede observar el diagrama de este módulo.

Figura 5.5: Módulo que realiza la división

- Una vez recibidos los dos operandos, el dividendo entra en el módulo

i\_round\_div que desplazará hacia la izquierda 5 bits.

- Tras el desplazamiento, se realiza la operación de división en el bloque *inversion*, con la particularidad de sumar 1 al bit 0 debido a que sólo en el caso de que haya acarreo, el bit 1 pasa a valer 1.

- Después el bloque round\_right realiza un desplazamiento de 1 bit hacia de la derecha. Esto se ha implementado de esta forma debido a que se opera en punto fijo³.

Poniendo un ejemplo del funcionamiento de la división, supóngase que se quieran dividir los números 4.125 y 5.125. Su representación en notación  $Q_{12,4}$  es:

$$4,125 = 0000000001000010 = 66_{(10)}$$

$5,125 = 0000000001010010 = 82_{(10)}$

Por lo tanto,

$$4,125/5,125 = 0,804878$$

que corresponde a

Interpretándolo como números enteros, la división corresponde a

$$66/82 = 0.804878$$

El problema que surge es que este valor no existe con esta representación, y con redondear mediante el método utilizado en la multiplicación no se consigue un valor correcto. Por lo tanto, es necesario buscar el valor más cercano realizando las siguientes operaciones:

<sup>&</sup>lt;sup>3</sup>Ver apéndice A

- 1. Se realiza el desplazamiento al dividendo: 1000010 desplazado 5 bits a la izquierda nos da 100001000000.

- 2. Se realiza la división: 100001000000 / 1010010 = 11001.

- 3. Se sumam 1 al resultado: 11001 + 1 = 11010.

- 4. Se desplaza 1 bit hacia la derecha: el resultado es 1101, que en aritmética de punto fijo es 0.8125, por lo que se redondea al par más cercano.

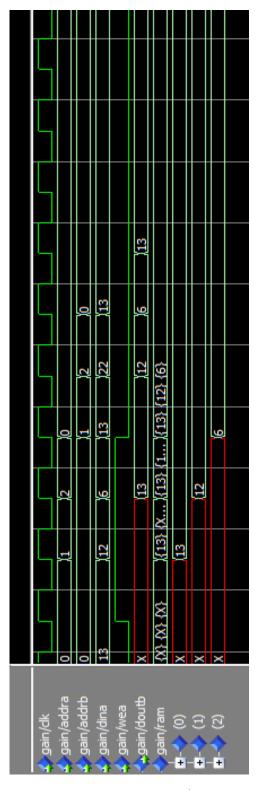

#### 5.3. Memorias RAM

Estas memorias de lectura y escritura permiten almacenar las diferentes matrices necesarias para los cálculos.

En el proyecto se han utilizado 3 tipos de memorias RAM:

- ram 3x1

- ram 3x3

Estas memorias son de doble puerto:

- El primero para la escritura, con las señales

- addra: dirección de escritura

- dina: dato de entrada

- wea: habilitación de escritura

- El segundo para la lectura, con las señales

- addrb: dirección de lectura

- doutb: dato de salida

No es necesaria una señal de capacitación de lectura de las RAM, ya que el hecho de proporcionar una dirección por el puerto de lectura hace que esta entregue los datos que contenga. El dato estará en la salida doutb un ciclo después de la llegada de la dirección.

La escritura se realiza mientras wea esté activada. En cada ciclo que esta señal esté activa se almacena el dato que esté en la entrada dina en la dirección proporcionada en la entrada addra.

El cronograma de la figura 5.6 ilustra las secuencias de acciones durante una escritura y posteriormente una lectura de la misma.

Como la ram\_3x1 puede almacenar hasta 3 elementos, no necesita más de 2 bits de direcciones para poder acceder a ellos. Por ello, todos los componentes con los que interactúa usan buses de 2 bits para la dirección, mientras que los componentes que interactúan con las ram 3x3 usan buses de 4 bits.

Figura 5.6: Cronograma de la escritura/lectura en una RAM

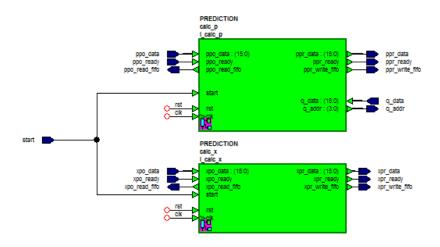

# Capítulo 6

# Módulo Prediction

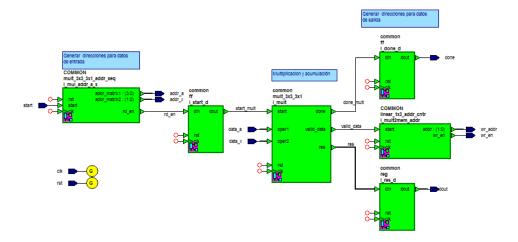

Este módulo implementa las ecuaciones del filtro correspondientes a la etapa de predicción:

$$\hat{x}_k = A\hat{x}_{k-1} \tag{6.1}$$

$$P_k^- = AP_{k-1}A^T + Q (6.2)$$

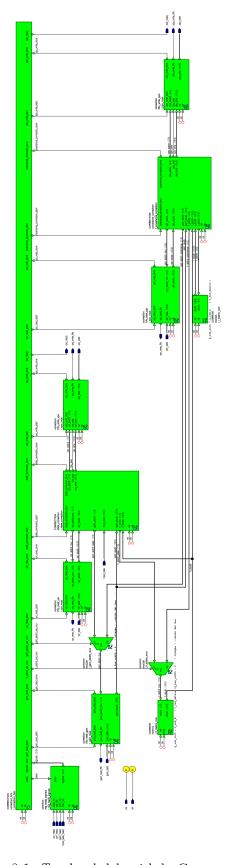

Puesto que las dos ecuaciones son independientes y se pueden calcular en paralelo, se ha descompuesto el módulo en dos submódulos (ver figura 6.1):

- $i\_calc\_x$ : implementa la ecuación 6.1.

- $i\_calc\_p$ : implementa la ecuación 6.2.

Figura 6.1: Top-level del módulo Prediction

En la tabla 6.1 se decribe la interfaz del módulo. La forma de agrupar estas señales en la tabla corresponde a las necesitadas para el correcto intercambio de información mediante la FIFO: para cada matriz intercambiada existe un bus de datos, una señal que avisa de la disponibilidad del dato y una señal de petición de lectura o escritura, según el caso. Las últimas tres señales, que no corresponden a información intercambiada, se propagan desde este módulo hasta el exterior del FK.

| Nombre                     | Tamaño         | Sentido                 | Comentario                                                                                                           |  |  |

|----------------------------|----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| xpo_data                   | 16 bits        | entrada                 | $ \begin{array}{c cccc} Viene & de & la & FIFO \\ i & correction 2 prediction & x. \end{array} $                     |  |  |

| xpo_read_fifo              | 1 bit          | salida                  | Activa lectura de datos de la FIFO.                                                                                  |  |  |

| xpo_ready                  | 1 bit          | entrada                 | Enviado por CORRECTION cuando XPO está en la FIFO.                                                                   |  |  |

| xpr_data                   | 16 bits        | salida                  | $egin{array}{cccc} Va & a & la & FIFO \\ i\_prediction2correction\_x. & & & & & & & & & & & & & & & & & & &$         |  |  |

| $xpr\_write\_fifo$         | 1 bit          | $\operatorname{salida}$ | Activa la escritura en la FIFO.                                                                                      |  |  |

| xpr_ready                  | 1 bit          | salida                  | Enviado a Correction cuando XPR está en la FIFO.                                                                     |  |  |

| ppo_data                   | 16 bits        | entrada                 | Viene de la FIFO                                                                                                     |  |  |

| ppo_read_fifo<br>ppo_ready | 1 bit<br>1 bit | salida<br>entrada       | i_correction2prediction_p. Activa lectura de datos de la FIFO Enviado por CORRECTION cuando PPO está en la FIFO.     |  |  |

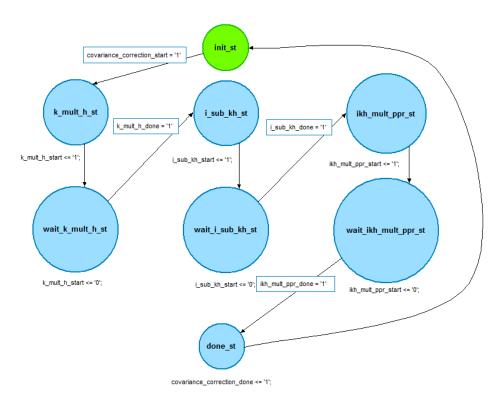

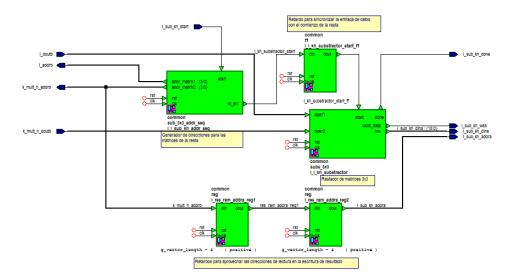

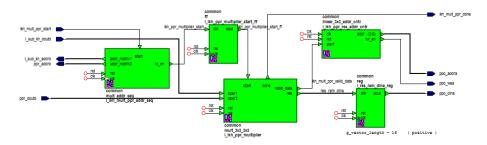

| ppr_data                   | 16 bits        | salida                  | $egin{array}{ccccc} Va & a & las & FIFOs \\ i\_prediction2correction\_p & y \\ i\_prediction2qain\_p. & \end{array}$ |  |  |