# ARM9Core

## Un emulador del procesador ARM9TDMI para PC

#### **Autores:**

Sergio Hidalgo Serrano Alberto Huerta Aranda Daniel Sañudo Vacas

**Profesor director:**

Katzalín Olcoz Herrero

**Curso Académico:**

2006/2007

### Resumen

El proyecto consiste en desarrollar el núcleo de un emulador para PC del microprocesador ARM9TDMI usado en sistemas empotrados, dispositivos portátiles, etc... Este proyecto está diseñado como una librería que se puede incorporar a una aplicación que necesite reproducir el comportamiento de un sistema basado en dicho procesador.

Su diseño permite la integración de forma sencilla junto con otros módulos que emulen las distintas partes del sistema, y a su vez facilita la incorporación de nuevas funcionalidades y características.

Dispone también de opciones para su uso en depuración de programas, tales como ejecución paso a paso, visualización y modificación del estado de la máquina, etc...

Dentro del proyecto también implementamos un programa de prueba que utiliza este núcleo para emular un sistema simple de depuración de programas, con el que hemos realizado diversos tests para comprobar el funcionamiento y rendimiento del emulador.

Un segundo objetivo del proyecto era el de estudiar una arquitectura real y las razones de las distintas decisiones tomadas durante su diseño, así como las mejores técnicas de emulación y sus ventajas e inconvenientes.

## **Summary**

Our project focuses in developing the core of an ARM9TDMI emulator for the PC. This microprocessor is commonly used in embedded systems, portable devices, etc... The project is designed to be added as a library into a bigger application which needs to reproduce an ARM-based system's behaviour.

Its design allows easy integration with other modules emulating the different system's parts, as well as simplifying the addition of new features and improved functions.

It also has options for its use while debugging other programs written for the ARM, such as step-by-step execution, full access to the machine's current state, etc...

Within the project we also developed a test program which uses the core to emulate a simple debugging system, which we used to test the proper working and performance of our emulator.

A second of goal for the project was to study a real processor architecture and the reasons behind the different design choices, along with the best emulation techniques and their weak and strong points.

## Organización de la memoria

A lo largo de este documento vamos a estudiar la estructura de la arquitectura ARM v4T (en concreto, del procesador ARM9TDMI), y sus características más importantes al nivel del proyecto. Además, explicaremos cuál es el proceso que se ha seguido a la hora de emular cada una de ellas, así como los detalles funcionales del emulador y del programa de prueba implementado.

En el primer capítulo hablaremos de las motivaciones y objetivos de este proyecto, así como las diferencias entre emuladores y simuladores, las principales técnicas de emulación, y las características generales del procesador emulado (ARM) y de la máquina sobre la que se ejecutará nuestro proyecto (x86).

En el segundo capítulo, examinaremos la estructura interna del emulador y las razones que llevaron a tomar las distintas decisiones en su diseño. Aprovecharemos también para comentar en detalle aspectos de la máquina real.

El tercer capítulo describirá a fondo cada uno de los grupos de instrucciones de la máquina real, su funcionamiento y posibles formatos, así como su correspondiente emulación.

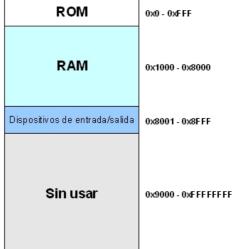

En el cuarto capítulo se describen las características que tiene el sistema de memoria y el emulador debe permitir, así como las técnicas que se han usado para reproducir su comportamiento.

El quinto capítulo está dedicado al tratamiento de interrupciones. Explicaremos su funcionamiento en la máquina real y el procedimiento que se ha seguido en su emulación.

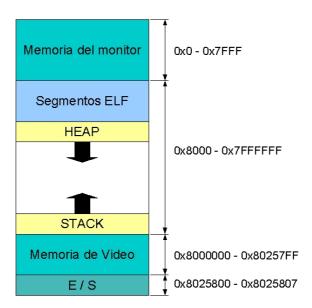

El programa de prueba realizado para comprobar la corrección y rendimiento del emulador será descrito en el capítulo seis, que también servirá como ejemplo práctico de cómo usar el ARM9Core en una aplicación mayor.

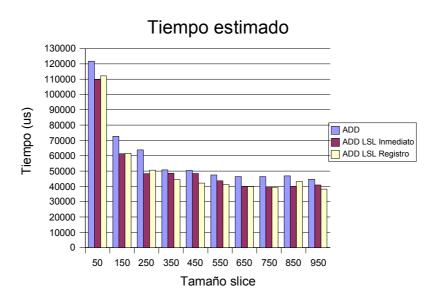

A continuación, en el séptimo capítulo, veremos un resumen de las distintas pruebas realizadas para medir el rendimiento del emulador bajo distintas configuraciones.

Y por último, el capítulo ocho estará dedicado a comentar las conclusiones obtenidas a lo largo del desarrollo del proyecto, y el trabajo que se podría hacer en el futuro para mejorarlo.

## Índice

| o  | Ribliografía                                          | 79   |

|----|-------------------------------------------------------|------|

| 8. | Conclusiones                                          | 76   |

|    | Test 6                                                | /4   |

|    | Test 6                                                |      |

|    | Test 4                                                |      |

|    | Test 2                                                |      |

|    | Test 1                                                |      |

| 7. | Tests y Estadísticas                                  |      |

| 6. | Programa de prueba                                    | 66   |

|    | 5.3 – Emulación de Interrupciones                     |      |

|    | 5.2 – Procesamiento de Interrupciones.                |      |

|    | 5.1 – Tipos de Interrupciones                         |      |

| 5. | Interrupciones                                        |      |

|    | Emulación                                             | . 55 |

|    | Descripción                                           |      |

| 4. | Sistema de Memoria                                    |      |

|    | 3.12 – Instrucciones de coprocesador                  |      |

|    | 3.11 – Interrupción por software                      |      |

|    | 3.10 – Transferencia de registro general a CPSR/SPSR  |      |

|    | 3.9 – Transferencia de CPSR/SPSR a registro general   |      |

|    | 3.8 – Branch with exchange.                           |      |

|    | 3.7 – Branch y Branch with link                       |      |

|    | 3.6 – Intercambio entre memoria y registro            |      |

|    | 3.5 – Transferencia de registro multiple              |      |

|    | 3.4 – Transferencia de media-palabra y byte con signo |      |

|    | 3.3 – Transferencia de una palabra y byte sin signo   |      |

|    | 3.2 – Multiplicación                                  |      |

| ٠. | 3.1 – Instrucciones Aritméticas y Lógicas             |      |

| 3  | Instrucciones ARM                                     | 26   |

|    | 2.3 – Bucle principal.                                |      |

|    | 2.2 – Contexto                                        |      |

|    | 2.1 – Esquema General                                 | . 13 |

| 2. | Funcionamiento del Emulador                           | 13   |

|    | 1.4 – Características del ARM v4T y del x86           | 10   |

|    | 1.3 – Intérprete vs. traducción binaria               |      |

|    | 1.2 – Emulador vs. simulador                          |      |

|    | 1.1 – Motivación                                      | 7    |

| 1. | Introducción                                          | 7    |

| Apéndice A - Listado de las instrucciones del ARM | 80 |

|---------------------------------------------------|----|

| Apéndice B - Comandos del programa de prueba      | 82 |

| Apéndice C – Tipos de datos del ARM9Core          | 84 |

| Apéndice D - Lista de métodos del ARM9Core        | 88 |

| Apéndice E - El formato ELF                       | 90 |

| Apéndice F - El protocolo ANGEL                   | 94 |

| Apéndice G - Herramientas GNUARM y SimIt-ARM      | 96 |

## 1. Introducción

#### 1.1 – Motivación

El proyecto consiste en desarrollar un emulador de la arquitectura ARM v4T, en concreto del microprocesador ARM9TDMI tipo RISC de 32 bits que se ejecutará sobre la plataforma Win32 en x86.

Los procesadores ARM son utilizados en sistemas empotrados, tales como dispositivos portátiles, videoconsolas, teléfonos móviles, calculadoras, etc... Actualmente, el 75% de los procesadores de 32 bits en este tipo de sistemas son modelos ARM, debido a su bajo consumo y alto rendimiento.

El mercado de dispositivos empotrados actualmente está en auge, aumentando el número de procesadores que se venden para estos usos cada año. Esta tendencia implica que el uso de los procesadores ARM es cada vez más popular, lo que les está convirtiendo en una de las arquitecturas más comunes en el panorama actual del desarrollo de aplicaciones.

Para el desarrollo de estas aplicaciones para el ARM muchas veces no se dispone de una máquina real donde poder realizar las pruebas necesarias para la depuración de las mismas. Esto significa que muchos desarrolladores deben recurrir a emuladores de la arquitectura para la cual trabajan, en nuestro caso, de la ARM v4T.

La mayoría de emuladores para esta plataforma son propietarios, y los emuladores libres y gratuitos no suelen incluir muchas características para su uso en depuración de programas en ejecución (acceso a la memoria, emulación de interrupciones, etc...). Por eso decidimos realizar un emulador libre diseñado tanto para la ejecución de programas nativos para la máquina real, como para tareas de depuración de nuevos programas (ejecución paso a paso, visualización y modificación de los registros y el estado de la máquina, etc...).

El emulador que desarrollamos es un módulo software que reproduce el comportamiento del core del microprocesador ARM9TDMI, y es capaz de integrarse con otros módulos que reproduzcan el comportamiento de otras partes del sistema (memoria, coprocesadores, interfaces de entrada y salida, etc...).

El objetivo de esto es que cualquier desarrollador pueda utilizar el "core emulado" en el marco de una aplicación mayor que necesite emular una plataforma completa basada en ARM.

El desarrollo de este proyecto también tiene como motivación el conocer en profundidad los detalles de la arquitectura. Además, el conocer una arquitectura real permite entender con más precisión el funcionamiento de un microprocesador, lo que simplifica el proceso de aprendizaje de futuras arquitecturas.

Dentro del proyecto, además del core del emulador, realizaremos un programa de prueba que reproduzca el comportamiento de una máquina genérica ARM y muestre tanto el funcionamiento de las características de depuración más comunes, como la integración del core dentro de una aplicación real.

#### 1.2 - Emulador vs. simulador

Reproducir el comportamiento de un procesador nos plantea un dilema: elegir entre un emulador o un simulador.

Un simulador tiene como objetivo reproducir el comportamiento interno del procesador, normalmente con motivos de aprendizaje de la arquitectura. Por tanto, un simulador intenta crear un "modelo" del procesador.

Por su parte, un emulador implica una visión externa del comportamiento de la máquina a emular. El objetivo en este caso es ejecutar programas reales tal y como lo haría la máquina real. Esto conlleva la necesidad de que el programa emulado se ejecute a la misma velocidad que tendría en el dispositivo físico, lo que impone grandes restricciones en cuanto a eficiencia.

Por tanto, a la hora de programar un emulador no es necesario reproducir la arquitectura física, sino que se considera al procesador como una caja negra: no importa como funcione internamente siempre que su comportamiento externo sea el mismo que el de la máquina real ante el mismo programa.

Por regla general, en un simulador se suele trabajar a nivel de ciclos, reproduciendo la arquitectura segmentada del procesador. Un emulador, en cambio, trabaja con una precisión a nivel de instrucción, por lo que se ignora dicho comportamiento segmentado.

Esto significa que mientras que el simulador muestra las dependencias de datos, paradas y bloqueos del pipeline, etc..., el emulador no se ve afectado por estas circunstancias. Por esto, el emulador es menos preciso que el simulador, pero mucho más rápido, lo que le permite ejecutar programas a la velocidad real.

La elección entre simulador y emulador condiciona por tanto toda la organización y estructura del programa, ya que los requisitos que se persiguen son completamente opuestos. Esto obliga a tener los objetivos muy bien definidos y saber escoger entre ambas perspectivas de acuerdo a lo que se busca.

En nuestro caso, los objetivos consistían en crear un programa capaz de ejecutar código ARM en tiempo real, lo que significa que buscamos eficiencia, aunque ello signifique una pérdida de precisión. Nuestro emulador funciona por tanto a nivel de instrucción, e ignora el comportamiento del pipeline segmentado.

## 1.3 - Intérprete vs. traducción binaria

A la hora de diseñar un emulador, se presentan dos posibles modelos: el de intérprete o el de traducción binaria.

El primer modelo, más simple, usa el mismo planteamiento que una máquina virtual, es decir, lee cada instrucción original y reproduce su comportamiento a través de una serie de rutinas escritas en el código de la máquina destino.

Por el contrario, la traducción binaria toma el código original y lo convierte en un código funcionalmente equivalente para la máquina destino en un primer paso de preprocesamiento. Posteriormente se ejecuta directamente el código traducido, eliminando así las penalizaciones que son comunes en los intérpretes.

Para realizar una traducción binaria en primer lugar se divide el código en bloques funcionales separados por instrucciones de salto. Cada bloque se ejecutará siempre del mismo modo, de forma que la traducción se realizará sobre bloques completos de código, dado que su comportamiento está ya determinado.

Al traducir un bloque el número de instrucciones obtenido suele ser distinto al número original. Esto es debido a que distintas arquitecturas pueden realizar ciertas operaciones con un número mayor o menor de instrucciones máquina. Sin embargo, al ser los bloques funcionalmente equivalentes, su ejecución dará siempre el mismo resultado.

Los emuladores que se implementan sobre sistemas de traducción binaria suelen también incluir un intérprete, dado que en ciertas ocasiones no es posible la traducción de algunas instrucciones de forma eficiente. Además, debido a las diferencias entre las distintas arquitecturas, resulta una tarea muy compleja desarrollar un traductor binario que genere código eficiente. Actualmente se sigue investigando y avanzando en este campo.

Una opción a medio camino entre interpretación y traducción binaria es la de la predecodificación. Este sistema consiste en realizar una primera pasada durante la inicialización del programa y extraer los distintos campos de las instrucciones para su almacenamiento en memoria.

De esta forma, al realizarse la ejecución de las distintas instrucciones, se evita la penalización por la decodificación de las mismas. El inconveniente de este sistema, además de un mayor consumo de memoria, se presenta al tener código que se automodifica.

En estos casos, es necesario llevar un control de las palabras de memoria que corresponden a instrucciones y han sido modificadas, mediante algún tipo de "cache de instrucciones". Esto significa que en estos casos se producirán penalizaciones en tiempo de ejecución.

En nuestro proyecto optamos por no implementar estos sistemas debido a restricciones de tiempo. Nuestro emulador será por tanto un intérprete con decodificación de instrucciones en tiempo de ejecución.

## 1.4 - Características del ARM v4T y del x86

A la hora de diseñar un emulador es necesario conocer las principales características tanto de la máquina cuyo comportamiento se desea reproducir (a la que llamaremos "máquina original"), como del procesador sobre el que se ejecutará dicho emulador (al que llamamos "máquina destino").

En nuestro caso, la máquina original se corresponde con la arquitectura v4T del ARM (ARM9TDMI) y la máquina destino con la familia x86 de Intel.

El conocer las características de ambos permite saber qué operaciones son más eficientes en la máquina destino, y por tanto deben ser aprovechadas para implementar el comportamiento de la máquina origen. También con esto se conoce las operaciones más frecuentes en la máquina origen, que deberán ser emuladas de manera eficiente.

En muchos casos se presentan similitudes en el comportamiento de ciertas características en ambas máquinas. Esto significa que si se consigue aprovechar esta similitud será posible una emulación mucho más eficiente que si fuera necesario implementar estos comportamientos manualmente.

Por ejemplo, tanto el ARM como el x86 presentan comportamientos similares en algunos de sus bits de estado (flags). Si en el emulador se consigue aprovechar esta característica se podría evitar el cálculo manual de los bits de estado, que es una operación costosa y común. De esta forma se utilizan los propios flags de la máquina destino como flags de la máquina original.

#### Características del ARM:

Dispone de dos repertorios de instrucciones distintos: uno de 32 bits (ARM) y otro de 16 (Thumb). De ellos, nuestro emulador sólo implementa el repertorio ARM.

El repertorio ARM permite a un programa tener el máximo rendimiento con el menor número de instrucciones, mientras que el repertorio Thumb es más simple pero ofrece más densidad de código y optimización de espacio.

Se puede cambiar el repertorio durante la ejecución con una instrucción o modificando el flag correspondiente.

A nivel físico, las instrucciones del repertorio Thumb son convertidas en las equivalentes del repertorio ARM.

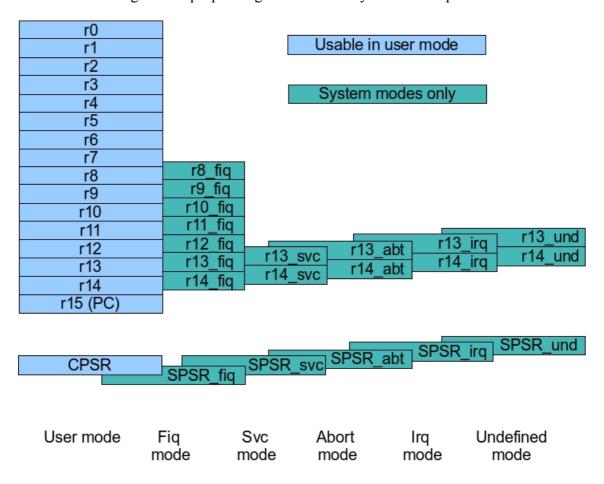

El ARM tiene 31 registros de propósito general de 32 bits, de los cuales 16 son visibles al programador al mismo tiempo. De entre ellos:

- Registro 13: Puntero a pila (SP).

- Registro 14: Dirección de retorno de subrutina (LR).

- Registro 15: Contador de programa (PC).

- Registro de estado (CPSR) y una copia del mismo (SPSR) por modo de ejecución.

Todos los registros son visibles en ambos modos (ARM o Thumb).

El ARM9TDMI es un procesador segmentado que presenta un pipeline dividido en 5 etapas:

- 1. Fetch.

- 2. Decodificación de instrucción y lectura de registros.

- 3. Ejecución de desplazamientos, ALU, cálculo de direcciones y multiplicaciones.

- 4. Acceso a memoria y multiplicación.

- 5. Escritura en registros.

Este procesador no dispone de anticipación de operandos, lo que significa que en el caso de producirse una dependencia de datos el pipeline entero quedará bloqueado.

Sin embargo, debido a que el emulador no tiene precisión a nivel de ciclo, el comportamiento del pipeline no es reproducido, pero es necesario tenerlo en cuenta en algunos momentos para asegurar que ciertas instrucciones se comportan de igual forma.

Todas las instrucciones ARM se ejecutan de forma condicional, dependiendo de un campo de condición que se compara con el valor de los bits de estado durante la fase de decodificación. Si no se cumple la condición, se salta a la siguiente instrucción del código.

Las instrucciones opcionalmente pueden actualizar los registros de condición (flags de la ALU: N, Z, C, V) de acuerdo al resultado.

Una de las principales características del ARM9TDMI es su desplazador de barril, que permite realizar desplazamientos y rotaciones de operandos sin apenas coste adicional. Esto implica que muchas de las instrucciones hacen uso de dicho elemento.

El ARM tiene 5 tipos de excepciones (interrupciones), a cada una de las cuales se le asocia un modo de ejecución. Cada modo dispone de un banco de registros lógicos que se corresponden a distintos registros físicos de entre los 31 disponibles.

Dispone de 4 tipos de instrucciones:

- Aritmético-lógicas

- Load / Store

- Branch (saltos)

- Instrucciones de coprocesador

#### Características del x86:

Esta arquitectura tiene un repertorio de instrucciones de 32 bits, a partir de i386 y superiores, aunque inicialmente era de 16 bits. Al contrario que el ARM, aquí no se dispone de ejecución condicional debiéndose utilizar instrucciones de salto para emularla. El repertorio ofrece instrucciones aritméticas, lógicas, de transferencia, misceláneas y de salto.

Se dispone de 4 registros de propósito general: EAX (Acumulador), EBX (Base), ECX (Contador) y EDX (Datos). Se proporciona acceso a los 32 bits, a los 16 bits menos significativos y a los dos bytes menos significativos de los registros anteriores.

Hay 4 registros de segmento de 16 bits que sirven para formar direcciones de memoria: CS (Código), SS (Pila), DS (Datos) y ES (Extra).

Existen además 2 registros de 32 bits para acceso indexado: ESI (Índice fuente) y DSI (Índice destino), y otros 2 registros de 32 bits que almacenan un puntero a la pila: ESP y EBP. El registro de 32 bits que apunta a la instrucción actual es el IP (Instruction Pointer). También existen una serie de registros especiales para control, test, debug...

El x86 posee indicadores de estado que toman sus valores según el resultado de las operaciones, siendo los siguientes:

- C: Carry

- O: Overflow

- S: Signo

- Z: Cero

- A: Carry Auxiliar, igual que Carry pero restringido al nibble (4 bits) bajo

- P: Paridad, indica si el resultado tiene una cantidad par de bits a uno

Cada uno de estos flags será modificado dependiendo del tipo al que pertenezca la instrucción x86, sin la posibilidad de indicar que se altere o no como en el ARM. Es decir, la instrucción de suma siempre cambiará el flag de signo según el valor del resultado obtenido.

La memoria usa una ordenación little-endian y permite accesos a direcciones no alineadas de 16 y 32 bits.

En la actualidad la gran mayoría de procesadores x86 incluye también el repertorio de instrucciones MMX, que permite operar con varios datos en una única instrucción (SIMD).

Esta extensión añade 8 registros de 64 bits (MM0-MM7), que pueden contener un dato de 64 bits, dos 32 bits, 4 de 16 bits u 8 de un byte (empaquetamiento). Estos registros realmente están solapados con los de la unidad de coma flotante (FPU), y cualquier modificación en estos alterará los otros.

A diferencia del ARM, el x86 no dispone de un desplazador de barril. Esto significa que la emulación de los desplazamientos de las instrucciones del ARM tendrá una penalización al ejecutarse sobre este procesador.

Debido a que el emulador busca la mayor eficiencia posible, y que se recurre en muchas ocasiones a integrar código en ensamblador junto con el código a alto nivel, es necesario tener en cuenta estas características de la máquina destino a la hora de implementar las distintas rutinas del mismo.

## 2. Funcionamiento del Emulador

## 2.1 - Esquema General

Basado en un diseño modular, el emulador ARM9Core puede ser incorporado en una aplicación que necesite reproducir el comportamiento del ARM9TDMI (arquitectura v4T) sobre un sistema Win32 ejecutándose en una plataforma x86.

Este requisito nos obliga a que el ARM9Core se distribuya como una librería para que el programador de la aplicación que lo vaya a usar pueda incluirlo en su propio proyecto. De esta forma, el usuario sólo necesitará programar el comportamiento de los subsistemas específicos de la máquina que desee emular, mientras que el ARM9Core le proporcionará el funcionamiento del microprocesador.

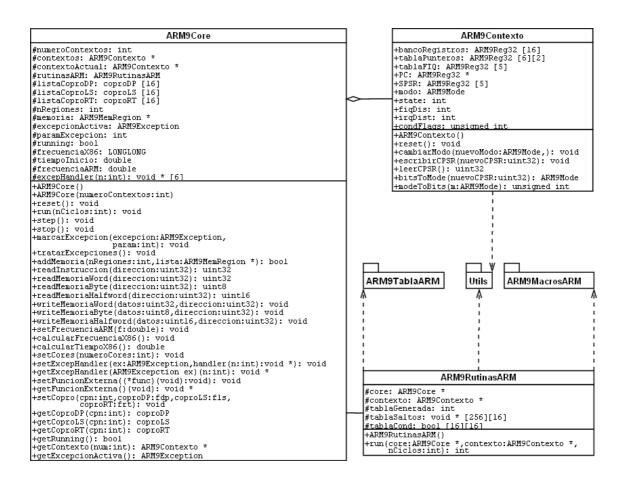

El proyecto está desarrollado para Win32 en Visual C++ 6.0, haciendo uso del ensamblador del x86 para conseguir el mayor rendimiento posible. El diseño está orientado a objetos, y se organiza de la siguiente forma:

#### **ARM9Core:**

Esta es la clase principal del proyecto. El usuario tendrá que instanciarla para poder hacer uso de las funciones del emulador. De esta forma esta clase actúa como interfaz con el resto de la aplicación.

#### **ARM9Contexto:**

El contexto representa el estado del procesador en un momento dado. El emulador puede reproducir el comportamiento de un sistema multinúcleo, en cuyo caso habría varios objetos de esta clase, donde cada uno representaría el estado de uno de los distintos núcleos.

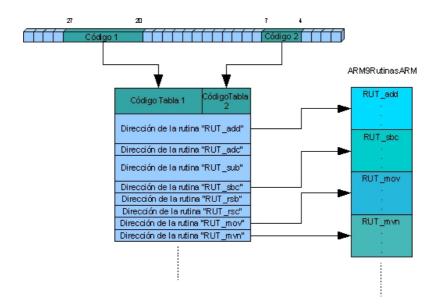

#### **ARM9RutinasARM:**

Esta clase contiene el código de las rutinas que reproducen el comportamiento de las instrucciones de 32 bits de la arquitectura ARM.

#### ARM9TablaARM:

Código que genera las direcciones de salto a cada una de las rutinas ARM según los campos comunes de un determinado tipo de instrucción.

#### **ARM9MacrosARM:**

Código que realiza tareas que tienen en común las diferentes rutinas ARM, tales como: comprobación de condición, obtención de operandos...

#### **Utils:**

Contiene definiciones de tipos y estructuras comunes utilizadas por las clases.

#### 2.2 - Contexto

El ARM9TDMI dispone de 7 modos de ejecución distintos:

- USER: Modo usuario, es un modo sin privilegios en el que se ejecutan las aplicaciones generales.

- **SVC:** Modo supervisor, es el modo en el que se ejecutan las interrupciones por software (SWI).

- ABORT: Este modo se activa para realizar el tratamiento de las excepciones que se producen al haber un fallo de acceso a memoria (DATA\_ABORT o PREFETCH\_ABORT).

- **UNDEFINED:** Modo indefinido, se activa al producirse una excepción por la lectura de una instrucción no existente en el repertorio.

- **IRQ:** Modo de tratamiento de interrupciones, se activa cuando se recibe una interrupción externa.

- **FIQ:** Modo de tratamiento de interrupciones rápidas, similar al anterior pero al disponer de más registros físicos permite una ejecución más eficiente.

- **SYSTEM:** Modo de sistema, similar al modo usuario pero con privilegios al acceder a regiones de memoria.

El procesador dispone de 31 registros de propósito general de 32 bits de los cuales solamente 16 son accesibles al programador en cada modo. Estos registros están distribuidos en bancos independientes, de forma que en modos distintos el mismo número de registro se corresponde a distintos registros físicos.

Esta disposición permite una ejecución más eficiente dado que al entrar en uno de estos modos con registros replicados no es necesario salvar en memoria los valores almacenados en los registros antiguos, porque estos ya son preservados.

Además de los registros de propósito general el ARM9TDMI dispone de un registro de 32 bits llamado CPSR (Current Program Status Register), y de 5 registros SPSR (Saved Program Status Register) distribuidos entre los distintos modos.

El CPSR guarda el estado actual del programa, con los siguientes campos:

- Modo de ejecución: 5 bits que codifican el modo de ejecución actual.

- Bit de estado: Discrimina entre el modo ARM o modo Thumb.

- Bit de desactivación de FIQ: Desactiva las interrupciones rápidas.

- Bit de desactivación de IRQ: Desactiva las interrupciones normales.

- Flags de condición: 4 bits que indican condiciones del resultado de la última operación que los haya activado.

- Flag N: Resultado negativo.

- Flag Z: Resultado cero.

- Flag C: Resultado con acarreo.

- Flag V: Resultado con desbordamiento en el bit de signo.

Los registros SPSR son similares al CPSR y se usan para preservar el estado de éste al cambiar de modo.

El registro 15 hace la función de contador de programa (PC), aunque también puede ser utilizado como registro de propósito general en la mayoría de las operaciones.

Para implementar el contexto contamos con una estructura ARM9Reg32 que representa un registro físico.

Esta estructura nos permite acceder al mismo en distintos formatos:

- Palabra de 32 bits con o sin signo.

- Media palabra de 16 bits con o sin signo.

- Acceso a los dos bytes más bajos de forma independiente con o sin signo.

- Acceso a los distintos bits del formato del registro CPSR/SPSR.

La implementación en C++ de este sistema se realiza usando la característica "union" que permite solapar distintos modos de acceso sobre el mismo dato físico.

El contexto implementa el banco de registros en su conjunto. En primera instancia se optó por tener 31 registros físicos y utilizar un array de 16 punteros que tomarían las direcciones de memoria de los 16 registros del modo actual. Al realizarse un cambio de modo era necesario actualizar este array con las nuevas direcciones.

Sin embargo, esto complicaba el acceso a los valores de los registros al producirse demasiadas indirecciones. Debido a esto, se decidió implementar otra solución que, si bien tiene una penalización mayor a la hora de cambiar de modo, es más eficiente a la hora de acceder a los datos.

Se disponen de 16 registros físicos ARM9Reg32 que se corresponden a los registros accesibles por el modo actual. Además de estos registros, existen otras tres tablas que guardan los valores de los bancos de registros que no están accesibles en este momento (registros del FIQ, registros 13 y 14, registros SPSR).

Al producirse un cambio de modo, se intercambian los contenidos entre los registros visibles y las tablas de los bancos de registros dependiendo del modo anterior y actual. Esto se implementa en el método cambiarModo de la clase.

Para acceder de forma eficiente a los datos del CPSR, este registro no se implementa como una estructura ARM9Reg32 debido a la penalización que tendría desempaquetar sus bits, dado que se usan con mucha frecuencia.

De este modo cada uno de los campos del CPSR se guarda de forma separada. A la hora de trabajar con el CPSR como un registro de 32 bits es necesario disponer de un método para reconstruirlo a partir de los campos independientes, y otro que haga el proceso inverso. Estos métodos están disponibles en la clase ARM9Contexto.

Por último esta clase también incluye un identificador de la última excepción marcada, para poder realizar las comprobaciones de prioridad.

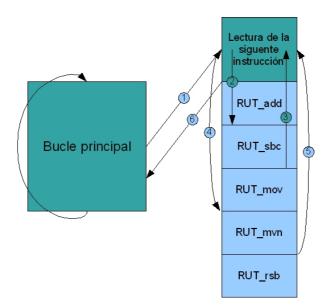

## 2.3 - Bucle principal

El ARM9Core funciona de forma secuencial. El flujo de ejecución del emulador se organiza en torno a un bucle que realiza los pasos correspondientes a la búsqueda, decodificación y ejecución de las instrucciones. Este bucle ejecuta grupos de instrucciones consecutivas durante un número determinado de ciclos ("slice"). Por cada slice se realizan las tareas de tratamiento de excepciones, sincronización y llamadas a funciones externas.

```

while (no fin ejecución) {

numero ciclos restantes = tamaño slice;

while (numero ciclos restantes > 0) {

ejecutar instrucciones (numero ciclos restantes);

tratar excepciones ();

}

sincronizar ();

función externa ();

}

```

Como se ve en el pseudocódigo anterior, el bucle más externo se repite hasta que se indica al emulador que termine su ejecución (normalmente desde la aplicación externa). En cada iteración se ejecuta a su vez un bucle interno encargado de la emulación del *slice* de tiempo (este *slice* viene determinado por una cantidad de ciclos que puede especificar el usuario).

La clase ARM9RutinasARM realiza la ejecución de las instrucciones hasta que o bien se acaba el *slice*, o bien se produce una excepción, en cuyo caso se trata y se repite el proceso con los ciclos restantes del *slice*.

Después de ejecutar cada *slice* se sincroniza la velocidad del emulador con la velocidad especificada por el usuario, y posteriormente se hace una llamada a la función externa. Esta función la implementa el usuario en su aplicación, de forma que éste pueda recuperar el control de la ejecución para realizar sus propias tareas (emulación de sistemas de entrada y salida, interrupciones externas, etc...).

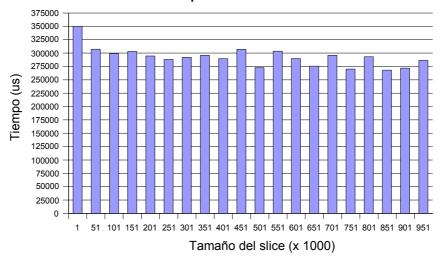

La razón de que las instrucciones se ejecuten en *slices* es para conseguir la mayor eficiencia posible. El código de emulación de rutinas es más eficiente cuanto mayor es el grupo de instrucciones consecutivas que se ejecutan, por tanto, la velocidad de ejecución será mayor para valores grandes del *slice*.

Por otra parte, la emulación de las interrupciones externas se realiza en la llamada a la función externa, que se hace únicamente cuando termina cada *slice*. Por tanto, la emulación de estas interrupciones será más precisa cuanto menor sea dicho *slice*.

El usuario tendrá que buscar un balance entre eficiencia y precisión, y ajustar los ciclos del *slice* de acuerdo a sus intereses. Como regla práctica se suele usar la frecuencia de la interrupción más rápida, que puede ser la señal de refresco de la pantalla, un temporizador, etc ...

Por ejemplo, si queremos emular un dispositivo portátil construido sobre un procesador ARM funcionando a una frecuencia de 25 Mhz, y que dispone de una pantalla que se refresca 50 veces por cada segundo (50 Hz), el tiempo de *slice* se podría calcular del siguiente modo:

50 Hz -> 1/50 segs entre cada dos actualizaciones de pantalla

25 Mhz =  $25*10^6$  ciclos por segundo  $25*10^6 / 50 = 500000$  ciclos de *slice*

#### Ejecución de instrucciones

El cuerpo interno del bucle principal transfiere el control a la clase de Rutinas encargada de la emulación del repertorio de instrucciones correspondiente.

Para ganar eficiencia el flujo de ejecución se mantiene siempre en el cuerpo de una misma y única función que contiene todo el código de todas las rutinas de emulación de las distintas instrucciones. Esto evita las penalizaciones por la creación y destrucción de los registros de activación cada vez que se invoca a una función, al realizar únicamente saltos entre distintos puntos de este código.

El primer paso al entrar en la rutina de tratamiento es la lectura de la siguiente instrucción apuntada por el PC. Aquí se accede a memoria para leer esta instrucción, se incrementa el contador del programa, y se salta al segmento de código encargado de emular dicha instrucción una vez sea identificada a través de sus campos comunes. Al terminar de emularla, se pasa a leer la siguiente mientras queden ciclos en el *slice*.

Dado el complejo repertorio de instrucciones del que dispone la arquitectura ARM v4T, con varios formatos posibles para una misma instrucción y alta carga semántica, la identificación de la instrucción leída se convierte en una tarea costosa. Con el objetivo de evitar el impacto que supondría hacer tantas comprobaciones como instrucciones existen, el ARM9Core dispone de una tabla precalculada de saltos.

Esta tabla almacena las direcciones de salto correspondientes al código de las rutinas que implementan las distintas instrucciones, indexadas a través de los campos de bits que permiten diferenciarlas. De esta forma, el proceso consiste en extraer estos campos de bits, y saltar directamente a la dirección que se almacena en la tabla de saltos para esa entrada.

Esta tabla se inicializa dinámicamente durante la primera ejecución de la primera instrucción a emular del programa. Esto provoca una penalización de tiempo en el primer *slice*, que se compensa más adelante al continuar la ejecución del programa.

La creación de la tabla no se realiza en la fase de compilación debido a la imposibilidad de determinar las direcciones de salto de dichas subrutinas en código C/C++. Para ello es necesario recurrir al ensamblador del x86, que al ejecutarse permite leer las etiquetas de salto y almacenar sus direcciones en la memoria:

```

__asm{

lea eax, etiqueta

mov direction, eax

}

tabla[entrada] = direction;

```

Como se ve en este ejemplo, la instrucción del x86 "lea" toma la dirección de la etiqueta y la almacena en un registro (eax), que luego es transferido a la variable "direccion". A partir de aquí, esta variable puede ser manipulada en código C/C++ tradicional.

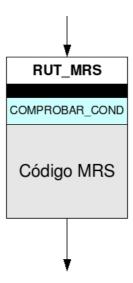

#### Ejecución condicional

Todas las instrucciones de la arquitectura ARM permiten la ejecución condicional. Esto es, se incluye un código de condición en cada una que se compara con los bits de estado actuales del procesador. Dependiendo del resultado, la instrucción se ejecuta o no. En caso de no ejecutarse, se trata como una "NOP" (consumiendo un ciclo) y se continúa por la siguiente.

Los posibles códigos de condición para las instrucciones son:

| Sufijo  | Descripción                  | Condición         |

|---------|------------------------------|-------------------|

| EQ      | Equal                        | Z = '1'           |

| NE      | Not Equal                    | Z = '0'           |

| CS / HS | Unsigned higher or same      | C = '1'           |

| CC / LO | Unsigned lower               | C = '0'           |

| MI      | Minus / Negative             | N = '1'           |

| PL      | Plus / Positive or zero      | N = '0'           |

| VS      | Overflow                     | V = '1'           |

| VC      | No overflow                  | V = '0'           |

| HI      | Unsigned higher              | C = '1' y Z = '0' |

| LS      | Unsigned lower or same       | C = '0' ó Z = '1' |

| GE      | Signed greater than or equal | N = V             |

| LT      | Signed less than             | $N \neq V$        |

| GT      | Signed greater than          | Z = 0' y N = V    |

| LE      | Signed less than or equal    | Z = '1' ó N ≠ V   |

| AL      | Always                       | Cualquiera        |

| NV      | Never (No usar)              | Ninguno           |

Estos 16 posibles códigos de condición se codifican siempre como los 4 bits más significativos de cada instrucción. A la hora de emular lo primero que debe hacer cada rutina es la comprobación para saber si debe o no ejecutarse.

Para agilizar este proceso, el ARM9Core utiliza una tabla precalculada de condiciones. Esta tabla tiene una entrada por cada posible valor de los flags de estado y de los bits de condición de la instrucción. De esta forma la rutina de emulación sólo tiene que consultar el valor de la tabla para los valores actuales, para saber si se debe ejecutar o no.

Dado que hay 16 posibles combinaciones tanto para los códigos como para los flags, el tamaño de la tabla es de 256 entradas, lo cual no es excesivo para la ganancia en eficiencia que se obtiene.

Esta tabla se genera al inicializar el emulador, por lo que a diferencia de la tabla de saltos, no se incurre en ninguna penalización para la primera ejecución.

#### Sincronización

Un emulador intenta siempre reproducir el mismo comportamiento externo de la máquina real. Esto quiere decir que un programa diseñado para esta máquina origen

debe ejecutarse también a la misma velocidad al ser emulado. De no ser así, programas que incluyan interfaces para el usuario se volverían inmanejables.

El ARM9Core permite al usuario especificar una frecuencia objetivo a la que quiere que la máquina emulada trabaje. Sabiendo esto y el número de ciclos por *slice*, el emulador es capaz de calcular el tiempo real que debería tardar dicho *slice* en ejecutarse.

La sincronización se hace entonces a nivel de *slice*. Se mide el tiempo que se ha tardado en ejecutarlo, y se compara con el tiempo objetivo deseado. Si se ha tardado menos, el emulador se detiene e introduce una espera hasta que ambos tiempos coincidan. De esta forma, la velocidad de emulación se corresponderá con la velocidad deseada.

En caso de que la frecuencia objetivo introducida sea muy alta, es probable que sea imposible alcanzarla. Si la emulación es más lenta, no se introduce espera alguna y se intenta ir a la velocidad más rápida posible.

Dado que los tiempos con los que se trabaja son del orden de los milisegundos es necesario disponer de un sistema de medida suficientemente preciso. Para ello el ARM9Core hace uso de las funciones de la API de Win32 "QueryPerformanceCounter" y "QueryPerformanceFrequency" que devuelven, respectivamente, el valor del contador de alta precisión del x86 y su frecuencia.

Estas funciones utilizan valores de 64 bits lo que permite obtener precisiones del orden de 10<sup>-9</sup> segundos (nanosegundos), lo cual es más que suficiente para nuestras necesidades.

El proceso de sincronización se realiza como muestra el siguiente ejemplo:

```

tiempoInicio = calcularTiempoActual();

EjecutarSlice ();

tiempo = calcularTiempoActual() - tiempoInicio;

//Sincronizacion

while (tiempo < tiempoObjetivo) {

Sleep (0);

tiempo = calcularTiempoActual() - tiempoInicio;

}</pre>

```

A la hora de calcular los ciclos consumidos para obtener el tiempo objetivo que debería ocupar el *slice* es necesario tener en cuenta durante la emulación de las instrucciones el número de ciclos que consume cada una de ellas. En el caso de que se ejecuten más ciclos de los especificados en el tamaño del *slice*, estos serán descontados en la siguiente iteración.

#### Emulación multinúcleo

El ARM9Core permite también la emulación de un sistema con varios núcleos (cores), cada uno con un contexto independiente. Todos ellos acceden a la misma memoria y se ejecutan a una misma frecuencia. Cuando se detiene el procesador también se detienen cada uno de los núcleos, de forma que siempre se ejecutan a la par.

Sin embargo, dado que el emulador es secuencial es necesario emular cada uno de los núcleos de forma consecutiva. Por tanto se ejecutan tantos *slices* como cores haya definidos. Por ejemplo, si se especifica un *slice* de 100000 ciclos y un procesador con 4 núcleos, cada iteración del bucle representará la emulación de 400000 ciclos (100000 por cada uno).

A la hora de sincronizar, se utiliza la medida del total de ciclos consumidos por todos los núcleos en conjunto.

Por último, todos los cores comparten los mismos métodos de tratamiento de excepciones.

## 3. Instrucciones ARM

## 3.1 – Instrucciones Aritméticas y Lógicas

#### Formato:

- <op>{<condición>} {S} Rd, Rn, #<valor inmediato de 32 bits>

- <op>{<condición>}{S} Rd, Rn, Rm, {<shift>}

- <op> puede ser cualquiera de las 16 instrucciones aritméticas

- <shift> especifica el tipo de desplazamiento, seguido de la cantidad (valor inmediato de 5 bits o registro)

## Descripción:

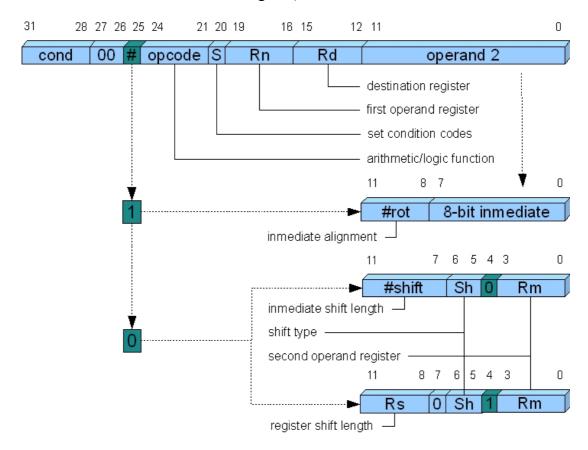

Las instrucciones aritméticas y lógicas (data processing) en la arquitectura ARM emplean un formato de 3 operandos: un registro destino y dos operandos fuente. De estos dos operandos fuente el primero siempre es un registro (Rn), mientras que el segundo puede ser otro registro (Rm) o un operando inmediato.

En el caso de que el segundo operando sea también un registro, el ARM permite aplicarle un desplazamiento antes de realizar la operación aritmética. Este desplazamiento puede venir dado por un valor inmediato de 5 bits o por un cuarto registro (Rs).

Todas las instrucciones aritméticas generan nuevos valores para los bits de condición, pero estos sólo se guardan si el bit 'S' de la instrucción está activado.

A partir de las posibles configuraciones que puede adoptar el segundo operando se obtienen los tres posibles formatos para las instrucciones aritmético-lógicas, y que aparecen en el mismo orden en la figura anterior:

```

DPI (Data Processing Inmediate): Operando inmediato

DPIS (D. P. Inmediate Shift): Registro desplazado por valor inmediato

DPRS (D. P. Register Shift): Registro desplazado por valor del registro Rs

```

Aunque todos los posibles formatos toman un registro destino y dos fuente, no todas las instrucciones aritméticas los usan. Por ejemplo, las instrucciones de transferencia de registros (MOV y MVN) ignoran el primer operando, y las instrucciones de comparación (TST, TEQ, CMP y CMN) no escriben en ningún registro destino.

Y por último, se puede especificar un mismo registro como destino y como fuente al mismo tiempo, así como usarlo simultáneamente para el primer y segundo operando, sin ninguna restricción.

#### **Operando Inmediato:**

La arquitectura ARM usa operandos de 32 bits. En el caso de usar un operando inmediato, sólo se disponen de 8 bits para codificar su valor. Pero dado que el ARM dispone de un desplazador de barril que le permite aplicar rotaciones a los operandos con una penalización de tiempo de ejecución nula, la arquitectura permite usarlo también con los operandos inmediatos.

De esta forma, se permite que el operando de 8 bits sea rotado por una cantidad par que también se especifica de forma inmediata en la propia instrucción. El valor por el que se desplaza al operando es el doble del indicado en el campo #rot, lo que permite cubrir los 32 bits posibles.

Esto es, en el ARM se puede especificar como operando inmediato cualquier número de la forma: [0-255] x 2<sup>2n</sup>

#### Registro desplazado:

Como hemos dicho antes, una de las características fundamentales de la arquitectura ARM es su desplazador de barril. El poder aplicar desplazamientos a los valores de los registros en cualquier instrucción aritmética sin apenas ninguna penalización da mucha versatilidad al repertorio, por lo que se convierte en una de las funciones más usadas por los programas diseñados para estos procesadores.

Estos desplazamientos nos permiten multiplicar por constantes pequeñas de forma mucho más eficiente que las instrucciones MUL. Por ejemplo, para multiplicar R0 por 5, podemos desplazarlo dos posiciones a la izquierda y sumarlo consigo mismo, como hace la siguiente instrucción:

```

ADD r0, r0, r0, LSL \#2; r0 := r0*5;

```

En este caso, se trata de una instrucción DPIS, puesto que la cantidad por la que desplazamos viene dada de forma inmediata (#2).

LSL indica que se realiza un desplazamiento a la izquierda. El ARM nos permite especificar distintos tipos de desplazamiento, que se codifican en el campo "Sh" de la instrucción:

- LSL (00): Desplazamiento lógico a la izquierda. Rellena con ceros.

- ASL (00): Desplazamiento aritmético a la izquierda. Igual que el anterior.

- LSR (01): Desplazamiento lógico a la derecha. Rellena con ceros.

- **ASR** (10): Desplazamiento aritmético a la derecha. Rellena con el signo del operando original (0 si positivo, 1 si negativo).

- **ROR** (11): Rota a la derecha. Al desplazar, el bit menos significativo que se pierde se usa para rellenar por la izquierda.

- **RRX** (11): Rota a la derecha una posición. El bit menos significativo se guarda como bit de carry, y el más significativo se rellena con el valor del carry antiguo.

Los desplazamientos ROR y RRX comparten la misma codificación (11). Para distinguirlos es necesario comprobar el valor de la cantidad (#shift). Como RRX siempre desplaza una única posición, no necesita usar este campo, que pone a cero. Si encontramos un valor distinto de cero, sabremos que estamos ante un ROR.

En el caso de que la instrucción no realice ningún tipo de desplazamiento, nos encontraremos con una codificación LSL #0 (es decir, todos los bits a cero). Saber esto es importante a la hora de emular, puesto que nos permite optimizar estos casos.

#### Uso de r15

Podemos especificar el registro del PC (r15) como operando fuente o destino en cualquiera de las instrucciones aritméticas. Si lo usamos como fuente, su valor será el de la dirección de la instrucción actual + 8, por el comportamiento del pipeline segmentado.

La única restricción es que no podremos tomarlo como segundo operando en el caso de tratarse de una instrucción DPRS.

En el caso de usarlo como destino, la instrucción aritmética se convierte en un salto. Esto también altera el comportamiento del bit 'S'. Si está activado, en lugar de actualizar los flags, el ARM copiará el valor del registro SPSR del modo actual sobre el CPSR.

Esta es una forma común de regresar de subrutinas e interrupciones. Por ejemplo, la siguiente instrucción se usaría para finalizar el tratamiento de una interrupción y restaurar el estado original de la máquina:

Esto copia el registro r14 (link register) al PC, haciendo que este último apunte de nuevo al lugar del código donde se produjo la interrupción, y restaura el CPSR, cambiando así el modo de ejecución del procesador y los bits de activación de interrupciones a sus valores originales.

#### Emulación:

A la hora de emular las instrucciones aritméticas del ARM nos encontramos con dos factores a tener en cuenta que toman una especial importancia y que son los que condicionan en gran medida la implementación: por una parte la gran carga semántica de las instrucciones y los distintos formatos posibles, que complican la decodificación, y por otra parte el efecto del desplazador en el rendimiento.

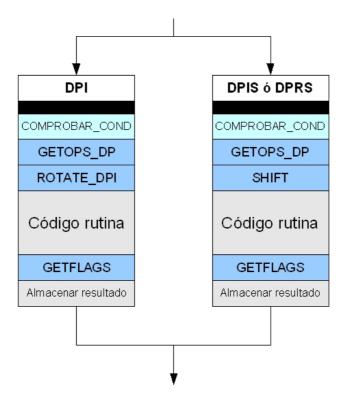

Inicialmente, y dado que los bits que permiten distinguir entre formatos (bits 25 y 4) aparecen en nuestras tablas de saltos, consideramos la opción de crear tres subrutinas para cada instrucción aritmética, una por cada formato posible que esa instrucción puede adoptar.

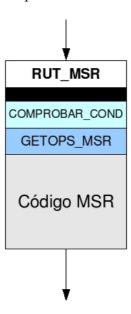

Tras considerar la complejidad de esa solución, optamos por tener una única subrutina por instrucción, pero con dos flujos de ejecución diferenciados dependiendo del formato: uno para las instrucciones DPI, y otro para las DPIS y DPRS; como se muestra en el siguiente diagrama:

COMPROBAR\_COND es la macro encargada de la ejecución condicional, y compara los bits de condición con los flags para determinar si la instrucción se ejecuta. Esto es común para todas las instrucciones.

En azul oscuro se indican las macros específicas de las instrucciones aritméticas. GETOPS\_DP es la encargada de decodificar la instrucción leída, y guardar los distintos operandos en variables para su uso posterior. Esta macro es común para ambos formatos, por lo que en ocasiones decodifica campos que no tienen sentido para el formato de la instrucción, aunque esto no supone un gran impacto en el rendimiento.

Los dos flujos de ejecución difieren a la hora de preparar su segundo operando. En el caso de las DPI, se usa la macro ROTATE\_DPI, que extrae el operando inmediato y lo rota por la cantidad indicada en la propia instrucción usando instrucciones del ensamblador del x86.

En el caso de las DPIS o DPRS se invoca a la macro SHIFT, que emula el comportamiento del desplazador de barril del ARM. Esta macro toma como entradas un valor (el contenido del registro Rm) y una cantidad (el valor inmediato o el contenido del registro Rs) ambas proporcionadas por GETOPS DP.

SHIFT comprueba el tipo de desplazamiento de la instrucción (el campo Sh) y ejecuta el código necesario para emular ese desplazamiento en el x86. Dado que las instrucciones del x86 tienen un comportamiento diferente a las del ARM para desplazamientos superiores a 31 bits, es necesario también detectar estos casos especiales y calcular directamente el resultado.

Si bien este tipo de desplazamientos es poco útil en la práctica, decidimos que merecía la pena emularlos correctamente puesto que algunos programas podrían recurrir a ellos. Por tanto, la penalización total de la emulación del desplazador es equivalente a una media de 5 instrucciones del x86 y dos o tres comparaciones condicionales.

Como comentábamos antes, en el caso de encontrarnos con un LSL #0 entendemos que no hay desplazamiento, por lo que no se ejecuta ninguna instrucción adicional. En ese caso, no hay penalización.

Independientemente de cuál de estas dos macros se ejecute, ambas tienen en común que al terminar almacenan el valor del primer operando en el registro EAX del x86, y el valor del segundo operando (debidamente calculado) en EBX. De forma que cada rutina específica para cada instrucción (ADD, SUB, etc...) puede ejecutar la operación correspondiente directamente sobre estos registros sin más complicaciones.

#### Emulación de los flags

Cualquier instrucción ARM puede modificar el valor de los flags del procesador activando el bit 'S'. La emulación de este comportamiento es crucial para que los programas se ejecuten correctamente. Como calcular manualmente los valores de estos flags para cada operación sería muy costoso, decidimos utilizar los flags del propio x86 para optimizarlo.

En concreto, tras la instrucción x86 que realiza la operación a emular incluimos una instrucción "pushf", que guarda el valor de los flags en la pila. La macro GETFLAGS es la que se encarga, si el bit 'S' está activado, de extraer estos valores y guardarlos en el contexto del emulador.

Sin embargo existen algunas diferencias entre el comportamiento de los flags en el x86 y el ARM. Por ejemplo, el bit de carry no toma los mismos valores en las operaciones de resta. Por ello, emulamos las restas como un complemento del segundo operando (o del primero) seguido de una suma. El valor del carry obtenido así es correcto, pero nos implica tener que generar el bit de overflow de forma manual, comprobando los signos antes y después de la operación.

Otro comportamiento especial de los flags del ARM está relacionado con el uso del desplazador de barril. Este desplazador puede generar su propio bit de carry, que es ignorado por las instrucciones aritméticas. Las instrucciones lógicas (AND, EOR, TST, TEQ, ORR, MOV, MVN, BIC) en cambio usan este valor como carry final.

Para emular esto, las macros ROTATE\_DPI y SHIFT guardan su propio carry en una variable auxiliar, que se escribe en el contexto o no dependiendo del tipo de instrucción.

Por último, la macro GETFLAGS también es la encargada de restaurar el CPSR con el valor del SPSR del modo actual si el registro destino es el PC, como comentábamos antes.

## 3.2 - Multiplicación

#### Formato:

```

32 bits:

MUL{<condición>}{S} Rd, Rm, Rs

MLA {<condición>} {S} Rd, Rm, Rs, Rn

64 bits:

<mul>{<condición>}{S} RdHi, RdLo, Rm, Rs

<mul> puede ser: UMULL, UMLAL, SMULL, SMLAL

31

24 23 21 20 19

8 7

4 3

28 27

16 15

12 11

0

S Rd/RdHi Rn/RdLo

0000

Rs

1001

cond

Rm

```

#### Descripción:

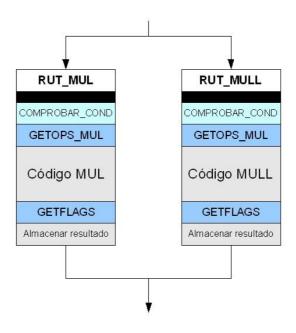

El ARM presenta dos tipos de multiplicaciones, con resultados de 32 bits (se pierden los 32 bits más altos), o de 64 bits (divididos en dos registros de 32, RdHi, el más significativo, y RdLo, el menos significativo).

Estas operaciones además permiten la multiplicación con acumulador (registro Rn para 32 bits o registros RdHi, RdLo para 64), y con o sin signo (sólo para 64 bits).

#### Emulación:

Decidimos separar la emulación en dos rutinas, una para las multiplicaciones de 32 bits y otra para las de 64:

GETOPS\_MUL es una macro común para obtener los operandos. El ensamblador del x86 proporciona una instrucción de multiplicación de 64 bits que, al igual que la del ARM, almacena la parte alta y baja del resultado en dos registros distintos de 32 bits.

Por tanto, el código de la rutina de 32 bits realiza una multiplicación y conserva únicamente el registro bajo del resultado, al que se le suma el valor del acumulador si es necesario.

Las multiplicaciones de 64 bits sin acumulador se emulan igualmente recurriendo a la instrucción del x86, y conservando esta vez ambos registros.

Sin embargo, el x86 no dispone de una suma de 64 bits, por lo que tras examinar varias alternativas, decidimos recurrir a las extensiones MMX, que son comunes en los procesadores actuales, para emular la multiplicación de 64 bits con acumulador.

De esta forma, tras llamar a la instrucción de multiplicación, usamos las MMX para montar los registros de 64 bits a partir de los dos de 32 donde se almacenó el resultado. Después realizamos la suma del acumulador (también montado en otro registro MMX), y desempaquetamos por último el resultado final sobre los dos registros de 32 bits.

Dado que la multiplicación del x86 también puede trabajar con o sin signo, no es necesario añadir más complejidad a nuestro código para emular este comportamiento.

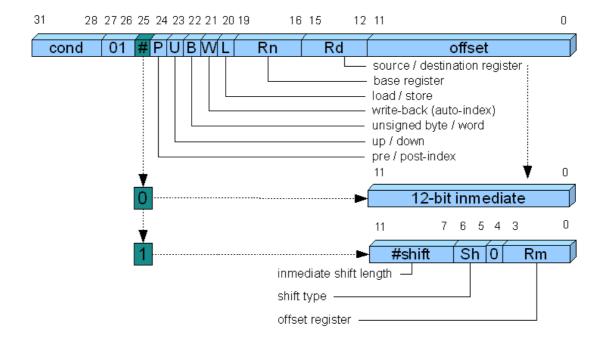

## 3.3 - Transferencia de una palabra y byte sin signo

#### Formato:

```

Forma pre-indexada:

```

LDR{<condición>}{B} Rd, [Rn, <offset>]{!} STR{<condición>}{B} Rd, [Rn, <offset>]{!}

#### Forma post-indexada:

LDR {<condición>} {B} {T} Rd, [Rn], <offset> STR {<condición>} {B} {T} Rd, [Rn], <offset>

#### Descripción:

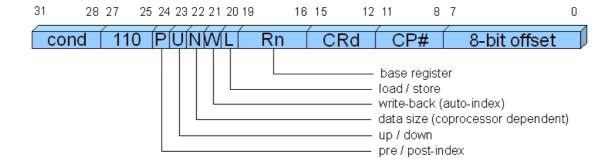

Estas instrucciones de transferencia de datos construyen la dirección de almacenamiento o carga a partir del registro Base (Rn) sumando o restándole un valor sin signo inmediato o el valor de un registro (Rm) posiblemente escalado.

Cuando un byte es cargado en un registro, éste es extendido con 0's hasta los 32 bits, y cuando el byte es guardado en la dirección de almacenamiento en memoria, éste corresponde a los 8 bits menos significativos del registro Rm (escalado o no).

En direccionamiento pre-indexado la dirección de memoria siempre es la combinación del registro Base y del desplazamiento y se calcula antes de realizar la transferencia. El registro Base solamente será actualizado con dicha dirección si el bit Write-Back está activo

Sin embargo, en post-indexado se utiliza solamente el valor del registro Base para la transferencia pero después siempre se almacena en el registro Base la combinación de su valor y el desplazamiento, independientemente del bit Write-Back.

#### Emulación:

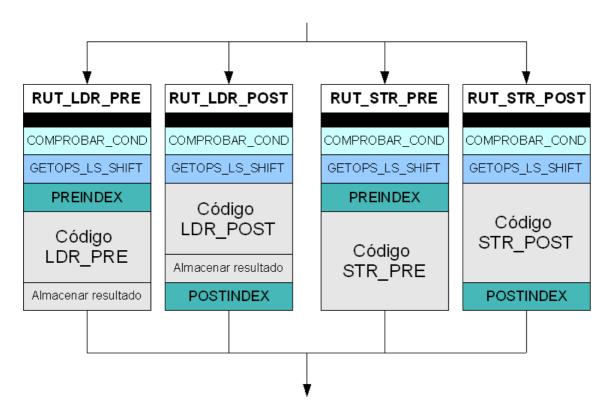

Para la emulación de estas instrucciones dividimos las rutinas a realizar según el tipo de instrucción (Load/Store) y el modo de direccionamiento (Pre/Post-indexado).

GETOPS\_LS\_SHIFT es la macro encargada (por medio de la macro interna GETOPS\_LS) de obtener el valor del registro Base, el registro destino/fuente, desplazamientos, tipo de la transferencia (palabra o byte), bit Write-Back y tipo de la combinación del registro Base con el desplazamiento, es decir, suma o resta. Si el registro Base es el registro 15 (o PC) el valor utilizado se verá incrementado en 4 bytes. Además el valor del desplazamiento será escalado (gracias a la macro SHIFT) si se detecta que el bit 25 de la instrucción es 1 o el desplazamiento es un registro.

Según el direccionamiento se llamará a la macro PREINDEX o POSTINDEX. Las dos calcularán la dirección efectiva (para la transferencia en la primera y para actualizar el registro Base en la segunda) sumando o restando el desplazamiento según el bit U de la instrucción. En PREINDEX si el bit Write-Back está activo se almacenará tal dirección en el registro Base.

En el código de la instrucción Load con direccionamiento pre-indexado (y post) si la transferencia es de un byte, cargaremos el byte desde la dirección efectiva de memoria. Para una palabra, alinearemos la dirección efectiva y cargaremos la palabra desde la dirección alineada\*. Si la palabra no estuviera alineada entonces la ajustamos, realizando las rotaciones necesarias en ensamblador de x86.

Esto también se hará de igual modo con el registro Base en post-indexado al acceder a memoria, y si se produce una excepción DATA ABORT no se cargará el valor en el registro en ambos casos. Sin embargo el registro Base sí se actualizará aunque se

<sup>\*</sup> Por dirección alineada nos referimos a direcciones que hacen referencia a una palabra de 32 bits o 4 bytes. Cualquier dirección cuyos dos últimos bits tengan un valor distinto de 0 se considerarán direcciones no alineadas.

produzca este tipo de excepción al leer de memoria o suceda un error al escribir en memoria.

Para las instrucciones Store, si la transferencia es de un byte, almacenaremos en la dirección efectiva de memoria los 8 bits menos significativos del registro fuente. Si la transferencia es de una palabra, la dirección efectiva será alineada de igual modo que en los Load, de forma que el valor del registro fuente será guardado en esta última dirección de memoria.

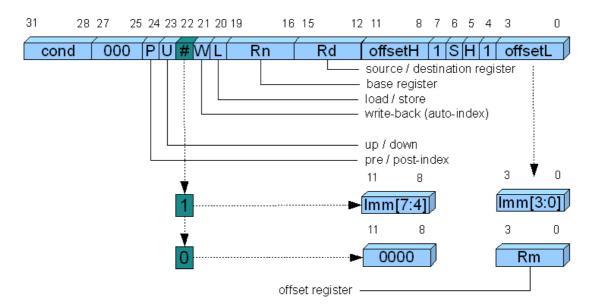

## 3.4 - Transferencia de media-palabra y byte con signo

#### Formato:

```

Forma pre-indexada:

```

LDR {<condición>}H|SH|SB Rd, [Rn, <offset>]{!} STR {<condición>}H|SH|SB Rd, [Rn, <offset>]{!}

#### Forma post-indexada:

LDR {<condición>} H|SH|SB Rd, [Rn], <offset> STR {<condición>} H|SH|SB Rd, [Rn], <offset>

## Descripción:

Este tipo de instrucciones es muy parecido a las de transferencia de datos de palabras y bytes sin signo pero en este caso el desplazamiento inmediato es reducido a sólo 1 byte y en el caso de que el desplazamiento sea un registro, su valor no puede ser escalado.

Para los Load de este tipo el dato puede ser byte con signo y media-palabra con y sin signo. Para los Store no importa el signo y se almacena media-palabra.

Cuando una media-palabra sin signo es cargada en un registro, éste es extendido con 0's hasta los 32 bits, y cuando es cargado un byte o media-palabra con signo, el registro es extendido hasta los 32 bits con el bit más significativo del dato.

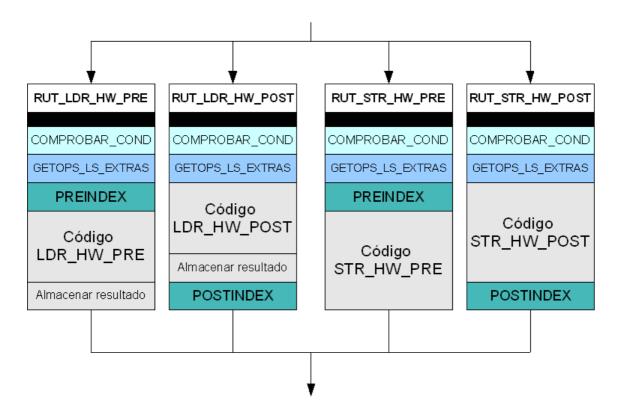

#### Emulación:

Al igual que la emulación de las instrucciones de transferencia de palabras y bytes sin signo, aquí también dividimos las rutinas a realizar según el tipo de instrucción (Load/Store) y el modo de direccionamiento (Pre/Post-indexado).

GETOPS\_LS\_EXTRAS es la macro encargada de obtener los campos comunes a todas las instrucciones (por medio de la macro GETOPS\_LS). En esta macro también se obtiene si el tipo de dato es byte con signo o media-palabra con y sin signo por medio de los bits 6 y 5 (S y H) para posteriormente acceder a memoria de forma apropiada. Si el bit 22 de la instrucción vale 1 entonces el desplazamiento es un valor inmediato de 1 byte que montamos mediante desplazamientos de bits usando los bits 11 a 8 como parte alta y los bits 3 a 0 como baja. Si es 0, el desplazamiento es el valor del registro Rm.

Para el código de la instrucción Load con direccionamiento pre-indexado se carga el byte con signo o media-palabra con o sin signo desde la dirección efectiva de memoria obtenida en la macro PREINDEX.

Con direccionamiento post-indexado se hará de igual modo desde la dirección de memoria indicada por el valor del registro Base.

Si el acceso a memoria provoca una excepción DATA ABORT entonces no se cargará el valor en el registro destino, pero sí se actualizará el registro Base.

Para las instrucciones Store simplemente almacenamos la media-palabra (con o sin signo) en la dirección efectiva de memoria o en la dirección de memoria indicada por el registro Base, según el tipo de direccionamiento.

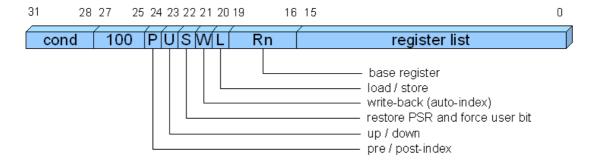

# 3.5 - Transferencia de registro multiple

#### Formato:

LDM {<condición>}<modo direccionamiento> Rn {!}, <registros {+ pc}>{^} STM {<condición>}<modo direccionamiento> Rn {!}, <registros>{^} <modo direccionamiento> puede ser: IA, IB, DA, DB, FD, ED, FA, EA.

## Descripción:

En este tipo de instrucciones cada bit de la lista de registros indica si el registro con índice igual a la posición de ese bit en la instrucción interviene en la transferencia. Es decir, si los bits 2, 5 y 8 de la lista de registros tienen valor 1, entonces los registros 2, 5 y 8 serán usados en la transferencia.

Los registros indicados en la lista serán cargados con las palabras que forman el bloque contiguo de memoria que comienza en la dirección del registro Base y se desplaza según el modo de direccionamiento en el caso de una operación Load. Para una operación Store las palabras de los registros indicados será almacenado en un bloque contiguo de memoria que comenzará en la dirección del registro Base y se desplazará según el direccionamiento. El valor del registro Base aumentará o decrementará antes o después de que una palabra se transfiera, y si el bit W está activo el registro Base se incrementará o decrementará con el número de bytes transferidos cuando se complete la instrucción.

Si el registro 15 (o PC) está en la lista de registros de un Load y el bit S está fijado entonces el SPSR del modo actual será copiado en el CPSR. Si el PC no está en la lista en un Load o Store ejecutados en modos distintos al modo usuario y el bit S está activo entonces se transfieren los registros del modo usuario.

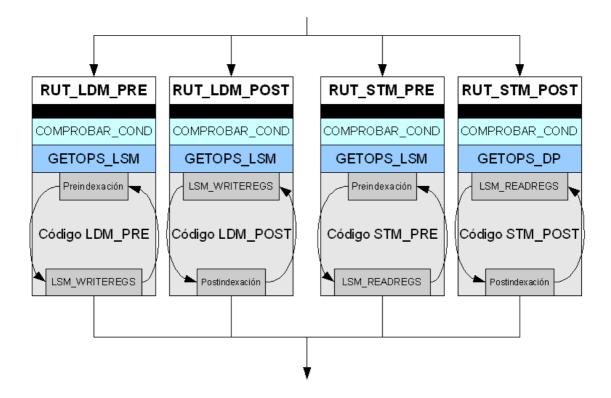

#### Emulación:

La emulación de estas instrucciones al igual que las de transferencias de registro 'simple' se dividen según el tipo de instrucción (Load/Store) y el modo de direccionamiento (Pre/Post-indexado).

La macro GETOPS\_LSM se encarga (por medio de la macro interna GETOPS\_LS) de obtener el valor del registro Base y el bit U. Si el registro Base es el registro 15 (o PC) el valor utilizado se verá incrementado en 4 bytes. Aquí el offset siempre es el mismo y es el tamaño de una palabra, 4 bytes. También obtenemos la lista de los registros que actuarán en la transferencia y alineamos el valor del registro Base si no lo está. Además comprobamos si el PC está en la lista y el bit S está activo para uso posterior.

Independientemente de que la instrucción sea Load o Store, de que el direccionamiento sea pre/post-indexado y de que la dirección efectiva se incremente o decremente después de cada transferencia, el registro con menor índice que tenga bit a 1 en la lista estará asociado con la dirección efectiva más baja que se produzca en la instrucción.

En el caso de Load esto indica que en dicho registro se cargará la palabra del bloque contiguo con dirección efectiva de memoria más baja. Y para el Store indica que la palabra del bloque contiguo con dirección efectiva de memoria más baja contendrá el valor de dicho registro.

De esta forma anterior es como vamos seleccionando y operando con cada uno de los registros destinos que tienen el bit a 1 en la lista.

Para los Load pre-indexados sumamos o restamos (según el bit U) el offset para calcular la dirección efectiva y con esta dirección obtenemos la palabra de memoria.

Justo aquí se llama a la macro LSM\_WRITEREGS que cargará la palabra obtenida en el registro destino actual. El registro destino actual puede ser el del modo actual u otro dependiendo de la siguiente política:

- PC no está en lista, bit S activo e índice del registro mayor igual que 8:

- Índice menor que 13 y modo actual FIQ -> Registro del banco FIQ.

- Índice menor que 13 -> Registro físico asociado al modo actual.

- Índice mayor igual que 13 -> Registro del banco del modo usuario.

- PC no está en lista ó bit S no activo -> Registro físico asociado al modo actual.

Si se ha producido una excepción DATA ABORT al obtener la palabra o el registro destino actual es el registro Base entonces no se escribirá sobre el destino. El registro Base siempre se actualiza con el valor del desplazamiento, y por tanto no se puede escribir sobre él.

En caso de Load post-indexado, realizamos la suma o resta del desplazamiento para calcular la dirección efectiva después de la macro LSM\_WRITEREGS.

Una vez hecha la carga de la palabra, repetiremos el proceso anterior hasta que hayamos examinado totalmente la lista de registros de la instrucción.

Finalmente si el bit W está a 1, actualizamos el registro Base con el número de bytes transferidos, y si el PC está en la lista y el bit S a 1, copiamos el SPSR del modo actual en el CPSR.

En los Store la situación es similar, salvo que almacenamos en memoria el valor de los registros que tengan bit a 1 en la lista, llamamos a la macro LSM\_READREGS para obtener valores de dichos registros y que sigue la misma política que la macro LSM\_WRITEREGS. Y en este caso no se copia el SPSR en el CPSR. Si sucedierá un error al grabar en memoria el registro Base sería igualmente actualizado.

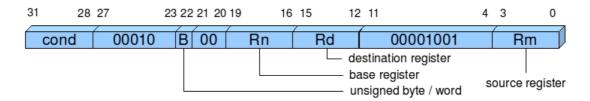

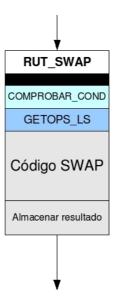

# 3.6 - Intercambio entre memoria y registro

## Formato:

SWP{<condición>} {B} Rd, Rm, [Rn]

## Descripción:

Las instrucciones de Swap combinan una instrucción de Load y otra de Store sobre una palabra, o sobre un byte sin signo.

La instrucción carga una palabra si el bit B=0, o un byte sin signo si B=1 de la dirección de memoria indicada en el registro Rn sobre el registro Rd, y guarda usando el mismo tipo de dato, el valor del registro Rm sobre la dirección de memoria indicada en Rn.

El registro 15 ( PC ) no debe utilizarse en ninguna de las codificaciones posibles de los 3 registros usados. El registro base Rn no debe ser el mismo que el registro Rm o el registro Rd.

## Emulación:

La emulación de esta instrucción se implementa sobre una misma rutina.

GETOPS\_LS es la macro encargada de obtener el valor del registro base (Rn), el valor del registro destino (Rd), el registro fuente (Rm), y el tipo de dato a transferir (bit B).

En el código de la rutina SWAP diferenciamos dos casos :

## - B = 1:

- Cargamos el byte sin signo de la dirección de memoria referenciada por Rn.

- Comprobamos si se ha producido un DATA\_ABORT, en cuyo caso pararíamos la ejecución de la instrucción y proseguiríamos con el tratamiento de dicha excepción.

- Guardamos en memoria el valor del registro Rm sobre la dirección de memoria referenciada por Rn.

#### - B = 0:

- Alineamos la dirección de memoria obtenida de Rn y cargamos la palabra referenciada.

- Comprobamos si se ha producido un DATA\_ABORT, en cuyo caso pararíamos la ejecución de la instrucción y proseguiríamos con el tratamiento de dicha excepción.

- Guardamos en memoria el valor del registro Rm sobre la dirección de memoria referenciada por Rn.

Por ultimo guardamos el valor cargado de memoria en el registro Rd.

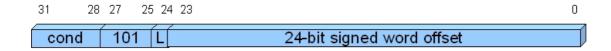

# 3.7 - Branch y Branch with link

## Formato:

B{L}{<condicion>} <dirección destino>

## Descripción:

Esta instrucción provoca que el PC salte a otra posición de memoria y continue ejecutando a partir de ella. La dirección se calcula a partir del operando inmediato extendido y desplazado a la izquierda de forma que apunte a una palabra alineada, que se suma al valor actual del contador de programa.

Cuando el bit L está activo, la dirección siguiente al salto es almacenada en el registro 14 del modo actual del procesador (link register).

La instrucción siguiente a la instrucción de salto no se ejecuta, ya que el ARM no dispone del modelo de salto retardado.

## Emulación:

El ARM9Core emula esta instrucción con una única rutina. A diferencia de otros procesadores, las instrucciones de salto del ARM no necesitan comprobar los códigos de condición para decidir si se realiza el salto, ya que se utiliza la ejecución condicional para simular este comportamiento.

Esto simplifica la tarea de emulación, de forma que lo único que hay que hacer es calcular la nueva dirección y guardar el registro link si el bit L está activo. Es necesario también corregir la dirección restando 4 bytes a la que calcula el ARM por motivo de la segmentación.

# 3.8 - Branch with exchange

### Formato:

## Descripción:

Esta instrucción está permitida únicamente en ARMs que soportan el formato de instrucción THUMB (16-bit) y permite cambiar el formato de instrucción a ejecutar entre ARM y THUMB.

El bit 0 del registro Rm es copiado al bit T del registro CPSR. Si Rm[0] = 1 cambia a modo THUMB y copia el valor del registro Rm con Rm[0] = 0 al PC, de esta forma provoca un salto a una dirección alineada a media palabra. Si Rm[0] = 1 cambia a modo ARM y copia el valor del registro Rm con Rm[1] = 0 al PC, de esta forma provoca un salto a una dirección alineada a una palabra.

## Emulación:

La emulación de esta instrucción se ejecuta sobre una misma rutina sin uso de macros externas encargadas de partes de la implementación de la instrucción.

Primero obtenemos el valor del registro que contiene la dirección del salto y después saltamos a la dirección de memoria indicada. Dado que nuestro emulador no soporta el modo Thumb, esta instrucción nunca cambia de modo.

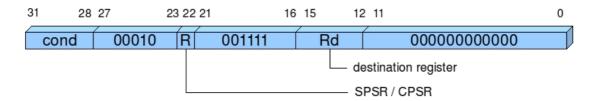

# 3.9 - Transferencia de CPSR/SPSR a registro general

## Formato:

MRS {<condición>} Rd, CPSR | SPSR

## Descripción:

Esta instrucción copia el valor del CPSR (R = 0), o el valor del SPSR (R = 1) a un registro general (Rd).

No es posible usar la transferencia del SPSR a un registro general en modo usuario, o en modo sistema, ya que estos modos carece de un SPSR.

Estas instrucciones se usan comúnmente para guardar los valores del CPSR y SPSR del modo actual a un registro general y poder modificarlos, para después restaurar el valor con la instrucción MSR.

#### Emulación:

La emulación de esta instrucción se ejecuta sobre una misma rutina, sin uso de macros externas encargadas de partes de la implementación de la instrucción.

En primer caso si el bit R = 0, almacenamos en el registro destino (Rd) el valor del CPSR. Para leer el CPSR hacemos uso del método leerCPSR. Éste compone los valores

de los campos del CPSR del contexto actual sobre un registro ARM9Reg32 para después realizar operaciones sobre él tratándolo como un entero.

En caso de que el bit R = 1, comprobamos que no nos encontramos en modo usuario, o en modo sistema, para después almacenar en el registro destino (Rd) el valor correspondiente al SPSR del modo actual.

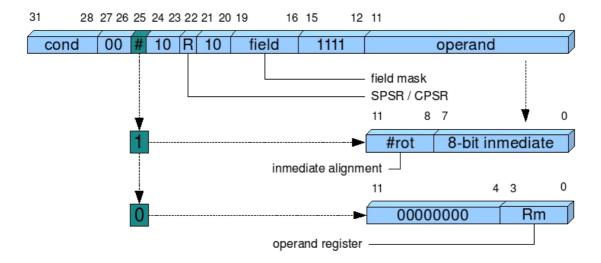

# 3.10 – Transferencia de registro general a CPSR/SPSR

#### Formato:

```

MSR {<condición>} CPSR_f | SPSR_f, #<32-bit inmediate>

MSR {<condición>} CPSR_<field mask> | SPSR_<field mask>, Rm

donde <field mask> es :

```

```

c – campo de control – *PSR[7:0].

```

x – campo de extensión – \*PSR[15:8]. (No se usa actualmente).

s – campo de estado – \*PSR[23:16]. (No se usa actualmente),

f – campo de flags – \*PSR[31:24].

## Descripción:

Esta instrucción carga en el CPSR o SPSR un operando inmediato de 8 bits rotado ( la rotación sigue el mismo proceso que para las instrucciones aritméticas y lógicas ), o el valor de un registro ( Rm ), los cuales han sufrido un proceso de enmascarado anteriormente.

El campo <field mask> determina cuales de los 4 bytes del PSR serán actualizados con los valores del registro Rm. En caso de usar un operando inmediato solo será posible actualizar los bits [31:24] del PSR. El bit 16 corresponde al PSR[7:0], el bit 17 corresponde al PSR[15:8], el bit 18 corresponde al PSR[23:16], y el bit 19 corresponde al PSR[31:24].

Los bits del PSR[31:24] son los únicos que pueden ser actualizados en modo usuario. El registro de estado a actualizar será el CPSR si R=0, o el SPSR si R=1. No se producirá ningún cambio sobre el CPSR o SPSR en caso de estar en modo usuario e intentar actualizar algún bit del 23 al 0.

<sup>\*</sup> PSR: representa tanto al CPSR como al SPSR.

No se permite modificar el SPSR en modo usuario, o modo sistema, ya que estos modos carecen de un SPSR.

Estas instrucciones se usan comúnmente para guardar en los registros de estado los registros de propósito general, modificados después de usar una MRS.

## Emulación:

La emulación de esta instrucción se implementa sobre una misma rutina.

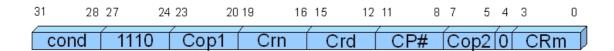

GETOPS\_MSR es la macro encargada de obtener el valor del registro operando Rm si el bit 25 = 0, o de rotar el valor inmediato, que será usado como operando, si el bit 25 = 1. También obtiene el valor del bit R y el valor del campo <field mask>.

Para R = 0, cargamos el valor del CPSR y actualizamos los 4 bytes del CPSR uno a uno, dependiendo del valor del campo <field mask> y el valor del operando. Una vez actualizados los 4 bytes del valor cargado del CPSR, sobrescribimos el CPSR con el nuevo valor. A la hora de escribir el valor del CPSR usamos el método escribirCPSR. Este método transforma el valor recibido a un registro ARM9Reg32 a partir del cual extraemos los valores correspondientes a los campos del CPSR del contexto actual. Después se procede a cambiar al nuevo modo.

En caso de que R=1, comprobamos que no nos encontramos en modo usuario, o en modo sistema, y repetimos el mismo proceso que para R=0, solo que esta vez actualizamos el valor correspondiente del SPSR del modo actual.

# 3.11 - Interrupción por software

#### Formato:

SWI{<condición>} <24-bit inmediate>

## Descripción:

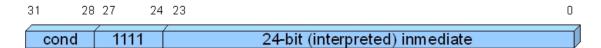

La instrucción SWI provoca una interrupción por software usadas por el sistema operativo comúnmente llamadas "supervisor call". Cambian el modo del procesador a modo supervisor y comienzan a ejecutar instrucciones a partir de la dirección 0x08. El campo inmediato de 24 bits no influye en las operaciones de la instrucción pero puede ser interpretado por el código del sistema.

En caso de que se cumpliera el código de condición :

- 1. Guarda la dirección de la instrucción siguiente a la SWI en r14 SVC.

- 2. Guarda el CPSR en el SPSR SVC.

- 3. Entra en modo supervisor y deshabilita las IRQs cambiando el CPSR[4:0] a 10011 y el CPSR[7] a 1.

- 4. Cambia el PC a 08 y comienza a ejecutar instrucciones a partir de esta dirección.

Después de ejecutar el código de la SWI la rutina del sistema restaura el valor del PC con r14 SVC y el CPSR con SPSR SVC.

#### Emulación:

La emulación de esta instrucción se ejecuta sobre una misma rutina sin uso de macros externas encargadas de partes de la implementación de la instrucción.

Primero se obtiene el valor del operando inmediato de la instrucción y después se hace uso del método marcarExcepcion (EXCEP\_SWI, operando) que provocará el tratamiento de la SWI. La documentación referente al tratamiento de todas las interrupciones se encuentra en el apartado 5.

# 3.12 - Instrucciones de coprocesador

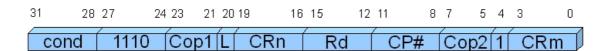

## Formato:

## Operaciones de datos de coprocesador :

CDP {<condición>} <CP#>, <Cop1>, CRd, CRn, CRm{, <Cop2>}

## Transferencia de datos de coprocesador:

Pre-indexed

LDC | STC {<condición>} {L} <CP#>, CRd, [Rn, <offset>] {!}

Post-indexed

LDC | STC {<condición>} {L} <CP#>, Crd, [Rn], <offset>

## Transferencias de registros de coprocesador :

De coprocesador a registros de ARM

MRC {<condición>} <CP#>, <Cop1>, Rd, CRn, CRm{, <Cop2>}

De registros de ARM a coprocesador

MRC {<condición>} <CP#>, <Cop1>, Rd, CRn, CRm{, <Cop2>}

## Descripción:

Las operaciones de datos de los coprocesadores son completamente internas al coprocesador y provocan modificaciones sobre sus registros (sumas, restas, multiplicaciones...). Un uso común son los coprocesadores de punto flotante encargados de realizar estas operaciones tan costosas.

Las operaciones de transferencia de datos de los coprocesadores permiten cargar o leer datos de la memoria del coprocesador. Desde que los coprocesadores pueden soportar su propio tipo de datos, el número de palabras transferidas son determinadas por el propio coprocesador. El ARM calcula la dirección de memoria y el coprocesador transfiere las palabras necesarias.

Las operaciones de transferencia de registros de los coprocesadores permiten transferir registros del ARM al coprocesador y viceversa.

## Emulación: